# 3 Channel 200mA/CH Automotive Linear LED Driver with Thermal Balancing

Datasheet (EN) 1.0

### **Product Overview**

The NSL21630/1 is an automotive-grade three-channel linear constant current LED driver, with up to 200mA current capability per channel. Wide supply voltage up to 40V enables NSL21630/1 a good fit for automotive battery directly powered application.

For linear-type constant current LED driver, thermal dissipation limit is a common issue to prevent it to be applicable for larger current or more channel-counts conditions. By implementing a unique thermal balancing design, the NSL21630/1 device is able to enlarge the output current capability with an automatic power balancing loop between the output channel and the external shunt resistor. It can address the thermal dissipation limit issue effectively with the majority of power conducted on the external shunt resistor, instead of the device itself.

The NSL21630/1 is able to support full diagnostics including the LED open-load and short-to-GND detection. With different FAULT bus connections, the NSL21630/1 can realize either "all off if one fails" or "others remain on if one fails".

# **Key Features**

- AEC Q-100 Qualified for Grade 1: T<sub>A</sub> from -40 °C to 125 °C

- 5 V to 40 V wide supply voltage range

- Three high accuracy constant current channels:

Automatic thermal balancing between device and external shunt resistors

Up to 200mA per channel current capacities

Individual current setting by channel

Individual PWM control by channel

Low dropout voltage: 450mV maximum at 100mA

Independent EN control pin to enable/disable device for low power operation

RoHS & REACH Compliance

• Full protections and diagnostics:

LED open-load detection with auto-recovery and adjustable enable threshold

LED short-to-GND detection with auto-recovery

Flexible FAULT bus connection options: "all off if one fails" and "others remain on if one fails"

Thermal shutdown

# **Applications**

- Automotive exterior rear lighting: position light, fog light, stop & tail light

- Automotive miscellaneous exterior lighting: center high mounted stop lamp, daytime-running lamp, turn indicator, door handle, blind spot detection indicator

- Automotive interior lighting: reading lamp, overhead console

### **Device Information**

| Part Number | Function<br>Description | Package   | Body Size           |  |  |

|-------------|-------------------------|-----------|---------------------|--|--|

| NSL21630    | Without EN              | HTSSOP-16 | 5mm x 4.4mm         |  |  |

| NSL21631    | With EN                 | H1330F-10 | 3111111 X 4.4111111 |  |  |

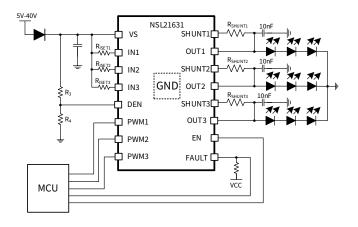

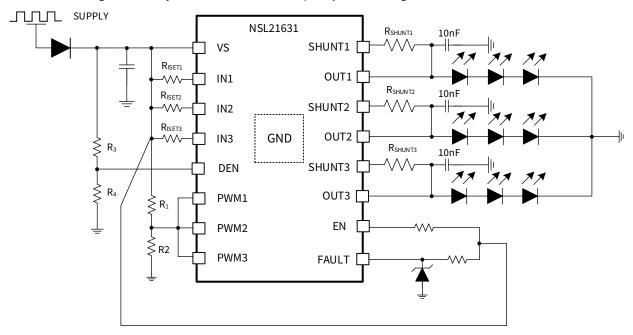

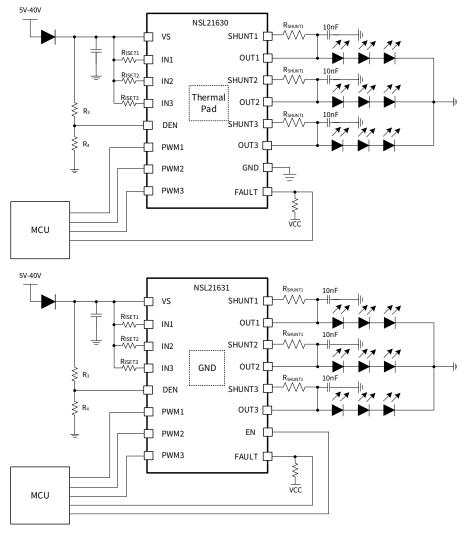

# **Typical Application**

# **INDEX**

| 1. PIN CONFIGURATION AND FUNCTION      |    |

|----------------------------------------|----|

| 2. ABSOLUTE MAXIMUM RATINGS            |    |

| 3. ESD RATINGS                         | (  |

| 4. RECOMMENDED OPERATING CONDITIONS    | (  |

| 5. THERMAL INFORMATION                 |    |

| 6. SPECIFICATIONS                      |    |

|                                        |    |

| 6.1. ELECTRICAL CHARACTERISTICS        |    |

| 6.3. PARAMETER MEASUREMENT INFORMATION |    |

| 7. FUNCTION DESCRIPTION                | 12 |

| 7.1. OVERVIEW                          | 1′ |

| 7.2. SYSTEM DIAGRAM                    |    |

| 7.3. FEATURE DESCRIPTION               |    |

| 7.3.1 POWER SUPPLY                     | 14 |

| 7.3.1.1 POWER ON RESET (POR)           | 14 |

| 7.3.1.2 ON AND OFF                     | 14 |

| 7.3.2 OUTPUT CURRENT SETTING           | 14 |

| 7.3.3 OUTPUT CURRENT THERMAL BALANCING | 14 |

| 7.3.4 LED BRIGHTNESS DIMMING           | 14 |

| 7.3.4.1 PWM CONTROL                    | 14 |

| 7.3.4.2 POWER SUPPLY CONTROL           | 15 |

| 7.3.5 PROTECTIONS AND DIAGNOSTICS      | 16 |

| 7.3.5.1 OPEN-LOAD DETECTION            | 16 |

| 7.3.5.2 SHORT-TO-GND DETECTION         |    |

| 7.3.5.3 THERMAL SHUTDOWN               | 16 |

| 7.3.5.4 FAULT BUS                      |    |

| 7.4. DEVICE OPERATION MODE             |    |

| 7.4.1 NORMAL OPERATION                 |    |

| 7.4.2 UNDERVOLTAGE LOCKOUT(UVLO)       |    |

| 7.4.3 LOW DROPOUT OPERATION            |    |

| 7.4.4 FAULT OPERATION                  | 18 |

| 8. APPLICATION                         | 18 |

| 8.1 TYPICAL APPLICATION CIRCUIT        | 18 |

| 8.1.1 SIMPLE APPLICATION WITHOUT MCU   | 18 |

| 8.1.1.1. DESIGN INFORMATION            | 19 |

| 8.1.1.2. DESIGN PROCEDURE              | 19 |

| 8.1.2 APPLICATION WITH MCU             | 20 |

| 8.1.2.1 DESIGN INFORMATION             | 20 |

| 8.1.2.2 DESIGN PROCEDURE               | 20 |

| 9. LAYOUT                              | 2  |

| 9.1. LAYOUT GUIDELINES                 |    |

| 9.2. LAYOUT EXAMPLE                    |    |

| 9.3. RECOMMENDED FOOTPRINT             | 23 |

|                                        |    |

# NSL21630/1

# Datasheet (EN) 1.0

| 10. PACKAGE INFORMATION       | 24 |

|-------------------------------|----|

| 11. ORDER INFORMATION         | 24 |

| 12. DOCUMENTATION SUPPORT     |    |

| 13. TAPE AND REEL INFORMATION |    |

| 14. REVISION HISTORY          |    |

# 1. Pin Configuration and Function

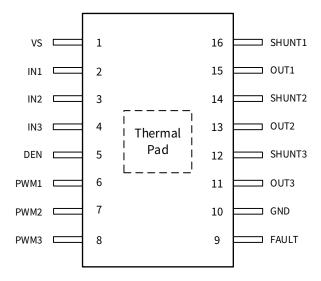

### **NSL21630**

Figure 1.1 NSL21630 Package

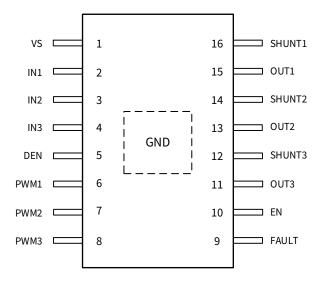

### **NSL21631**

Figure 1.2 NSL21631 Package

Table 1.1 HTSSOP-16 Pin Configuration and Description

| PIN NO. | SYMBOL | FUNCTION                          |

|---------|--------|-----------------------------------|

| 1       | VS     | Power supply pin                  |

| 2       | IN1    | Current input for OUT1 and SHUNT1 |

| 3       | IN2    | Current input for OUT2 and SHUNT2 |

| 4       | IN3    | Current input for OUT3 and SHUNT3 |

| PIN NO.     | SYMBOL                                              | FUNCTION                                                                                                                    |

|-------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 5           | DEN                                                 | Diagnosis enable for open-circuit detection. Can be used to avoid false open-circuit detection during low-dropout operation |

| 6           | PWM1                                                | PWM control input for OUT1 and SHUNT1, tie to GND if this channel is not used.                                              |

| 7           | PWM2                                                | PWM control input for OUT2 and SHUNT2, tie to GND if this channel is not used.                                              |

| 8           | PWM3                                                | PWM control input for OUT3 and SHUNT3, tie to GND if this channel is not used.                                              |

| 9           | FAULT                                               | Fault output                                                                                                                |

| 10          | GND NSL21630: Ground                                |                                                                                                                             |

| 10          | EN                                                  | NSL21631: Device enable pin                                                                                                 |

| 11          | OUT3                                                | Channel 3 output, tie to GND if this channel is not used.                                                                   |

| 12          | SHUNT3                                              | Channel 3 output with thermal balancing shunt resistor, tie to OUT3 if not used.                                            |

| 13          | OUT2                                                | Channel 2 output, tie to GND if this channel is not used.                                                                   |

| 14          | SHUNT2                                              | Channel 2 output with thermal balancing shunt resistor, tie to OUT2 if not used.                                            |

| 15          | OUT1                                                | Channel 1 output, tie to GND if this channel is not used.                                                                   |

| 16          | SHUNT1                                              | Channel 1 output with thermal balancing shunt resistor, tie to OUT1 if not used.                                            |

| Thermal Pad | Thermal NSL21630: Suggest to connect to GND mal Pad |                                                                                                                             |

|             | GND                                                 | NSL21631: Ground                                                                                                            |

# 2. Absolute Maximum Ratings

| Parameters           | Symbol                                   | Min                          | Max                  | Unit |

|----------------------|------------------------------------------|------------------------------|----------------------|------|

| Supply voltage       | VS                                       | -0.3                         | 45                   | V    |

| High voltage input   | DEN, PWM1, PWM2, PWM3, EN                | -0.3                         | V <sub>VS</sub> +0.3 | V    |

| High voltage input   | IN1, IN2, IN3                            | Max{V <sub>vs</sub> -1,-0.3} | V <sub>vs</sub> +0.3 | V    |

| High voltage output  | OUT1, OUT2, OUT3, SHUNT1, SHUNT2, SHUNT3 | -0.3                         | V <sub>VS</sub> +0.3 | V    |

| Fault report pin     | FAULT                                    | -0.3                         | V <sub>vs</sub> +0.3 | V    |

| Ambient temperature  | T <sub>A</sub>                           | -40                          | 125                  | °C   |

| Junction temperature | T,                                       | -40                          | 150                  | °C   |

| Storage temperature  | T <sub>stg</sub>                         | -65                          | 150                  | °C   |

# 3. ESD Ratings

|                         | Ratings                                           | Value | Unit |

|-------------------------|---------------------------------------------------|-------|------|

|                         | Human body model (HBM), per AEC-Q100-002-RevD     |       |      |

|                         | All pins                                          | ±2.0  | kV   |

|                         | • Corner pins(1,8,9,16)                           | ±2.0  | kV   |

| Electrostatic discharge | Charged device model (CDM), per AEC-Q100-011-RevB |       |      |

|                         | All pins                                          | ±500  | V    |

|                         | • Corner pins(1,8,9,16)                           | ±750  | V    |

# **4. Recommended Operating Conditions**

| Parameters          | Symbol                                      | Min | Тур                                | Max             | Unit |

|---------------------|---------------------------------------------|-----|------------------------------------|-----------------|------|

| Supply voltage      | VS                                          | 5   |                                    | 40              | V    |

| High voltage input  | IN1, IN2, IN3                               |     | V <sub>VS</sub> -V <sub>ISET</sub> |                 |      |

| High voltage input  | DEN, PWM1, PWM2, PWM3,<br>EN                | 0   |                                    | $V_{\text{VS}}$ | V    |

| High voltage output | OUT1, OUT2, OUT3,<br>SHUNT1, SHUNT2, SHUNT3 | 0   |                                    | V <sub>VS</sub> | V    |

| Fault report pin    | FAULT                                       | 0   |                                    | V <sub>VS</sub> | V    |

# 5. Thermal Information

| Parameters                                   | Symbol                     | HTSSOP-16 | Unit |

|----------------------------------------------|----------------------------|-----------|------|

| IC Junction-to-Air Thermal Resistance        | $\theta_{JA}$              | 45.8      | °C/W |

| Junction-to-case (top) thermal resistance    | $\theta_{	extsf{JC(TOP)}}$ | 40.6      | °C/W |

| Junction-to-board thermal resistance         | <b>Ө</b> ЈВ                | 21.2      | °C/W |

| Junction-to-top characterization parameter   | Ψлτ                        | 2.3       | °C/W |

| Junction-to-board characterization parameter | ψјв                        | 18.9      | °C/W |

| Junction-to-case (bottom) thermal resistance | $\theta_{JC(bot)}$         | 5.75      | °C/W |

# **6. Specifications**

### **6.1. Electrical Characteristics**

( $V_{VS}$  from 5 V to 40 V,  $T_J = -40$  °C to 150 °C unless otherwise noted)

| Parameters     | Symbol          | Condition | Min | Тур | Мах | Unit |

|----------------|-----------------|-----------|-----|-----|-----|------|

| Supply voltage | $V_{\text{VS}}$ |           | 5   |     | 40  | V    |

# NSL21630/1

| Parameters                                            | Symbol                 | Condition                                                                         | Min   | Тур  | Мах   | Unit |

|-------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------|-------|------|-------|------|

| Supply voltage POR<br>threshold<br>(Rising)           | $V_{\text{VS,TH1}}$    | V <sub>vs</sub> ramps up                                                          |       | 4.8  | 5     | V    |

| Supply voltage POR<br>threshold<br>(Falling)          | V <sub>VS,TH2</sub>    | V <sub>vs</sub> ramps down                                                        | 4.5   | 4.6  |       | V    |

| Shutdown current                                      | I <sub>SD</sub>        | V <sub>VS</sub> = 12 V, EN low                                                    |       | 11   | 15    | μΑ   |

|                                                       | ΙQ                     | PWMx high, EN high                                                                |       | 0.65 | 1     | mA   |

| Quiescent current                                     | I <sub>Q_FAULT</sub>   | PWMx high, EN high, FAULT externally pulled low                                   |       | 0.32 | 0.45  | mA   |

| [N input throshold                                    | V <sub>EN_H</sub>      | EN high level logic input                                                         | 2     |      |       | V    |

| EN input threshold                                    | V <sub>EN_L</sub>      | EN low level logic input                                                          |       |      | 0.7   | V    |

| EN internal pulldown current                          | I <sub>EN</sub>        | V <sub>EN</sub> = 12 V                                                            | 1.5   | 3.2  | 5     | μΑ   |

| DEN, PWM input threshold                              | $V_{Logic_H}$          |                                                                                   | 1.162 | 1.21 | 1.258 | V    |

| DEN, PWM input threshold                              | $V_{Logic_L}$          |                                                                                   | 1.066 | 1.11 | 1.154 | V    |

| Per channel current range                             | I <sub>CHx_MAX</sub>   | $I_{CHx\_MAX} = I_{OUTx} + I_{SHUNTx}$                                            |       |      | 200   | mA   |

| Regulated voltage on current setting resistor         | V <sub>ISET</sub>      |                                                                                   |       | 150  |       | mV   |

| Channel to channel matching                           | ΔV <sub>ISET_C2C</sub> | $\Delta V_{ISET\_C2C} = 1 - V_{ISET\_x}/V_{ISET\_AVG}$                            | - 4   |      | 4     | %    |

| Device to device matching                             | ΔV <sub>ISET_D2D</sub> | $\Delta V_{ISET\_D2D} = 1 - V_{ISET\_AVG}/V_{ISET\_NOM}$                          | - 5   |      | 5     | %    |

| Dropout voltage                                       | $V_{Dropout}$          | $V_{Dropout} = V_{INX} - V_{OUTx}$ , SHUNTX floating, $I_{SET} = 100 \text{ mA}$  |       | 240  | 450   | mV   |

| Ron of Switch FET in SHUNT loop                       | R <sub>SW</sub> _SHUNT | $R_{SW\_SHUNT} = (V_{IN} - V_{SHUNT})/I_{SET}$ , OUT floating, $I_{SET} = 100$ mA |       | 3    | 5.5   | Ω    |

| Channel open-load rising threshold                    | V <sub>OPEN,TH1</sub>  | V <sub>VS</sub> – V <sub>OUTx</sub>                                               | 300   | 430  | 550   | mV   |

| Channel open-load falling threshold                   | V <sub>OPEN,TH2</sub>  | V <sub>VS</sub> - V <sub>OUTx</sub>                                               | 200   | 300  | 390   | mV   |

| Channel short-to-ground rising threshold              | V <sub>SHORT,TH1</sub> | Voutx or Vshuntx                                                                  | 1.162 | 1.21 | 1.258 | V    |

| Channel short-to-ground falling threshold             | V <sub>SHORT,TH2</sub> | Voutx or Vshuntx                                                                  | 0.8   | 0.85 | 0.9   | V    |

| Channel open-load / short-<br>to-ground retry current | I <sub>O/S_Retry</sub> |                                                                                   | 0.6   | 1    | 1.3   | mA   |

| Channel open-load / short-<br>to-ground deglitch time | t <sub>O/S_Deg</sub>   |                                                                                   |       | 160  |       | μs   |

| FAULT logic input high threshold                      | V <sub>FAULT_IH</sub>  |                                                                                   | 2     |      |       | V    |

| FAULT logic input low threshold                       | V <sub>FAULT_IL</sub>  |                                                                                   |       |      | 0.7   | V    |

| FAULT logic output high voltage                       | V <sub>FAULT_OH</sub>  | With 2μA external pulldown                                                        | 4.9   | 5.3  | 5.5   | V    |

| FAULT logic output low voltage                        | V <sub>FAULT_OL</sub>  | With 2 mA external pullup current                                                 |       |      | 0.45  | V    |

| Parameters                                     | Symbol                 | Condition                                                                                                                                                                                                                                    | Min | Тур | Мах | Unit |

|------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| FAULT internal pullup current                  | I <sub>FAULT_PU</sub>  |                                                                                                                                                                                                                                              | 5   | 13  | 20  | μΑ   |

| FAULT internal pulldown current                | I <sub>FAULT_PD</sub>  | V <sub>FAULT</sub> = 0.5 V                                                                                                                                                                                                                   | 2   | 3   | 4   | mA   |

| FAULT leakage current                          | I <sub>FAULT_LKG</sub> | V <sub>FAULT</sub> = 40 V                                                                                                                                                                                                                    |     |     | 1   | μΑ   |

| Device thermal shutdown temperature            | $T_{SD}$               |                                                                                                                                                                                                                                              |     | 170 |     | °C   |

| Device thermal shutdown temperature hysteresis | T <sub>HYST</sub>      |                                                                                                                                                                                                                                              |     | 17  |     | °C   |

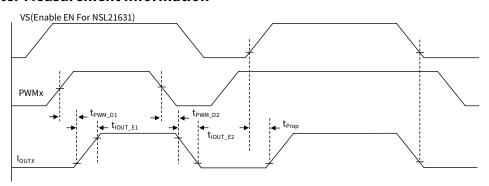

| PWM rising delay time                          | t <sub>PWM_D1</sub>    | From PWM rising edge to 10% of $I_{OUT}$ rising edge, $V_{VS}$ = 12 V, $V_{OUT}$ = 6 V, $I_{SET}$ = 100 mA                                                                                                                                   |     | 5   |     | μs   |

| PWM falling delay time                         | t <sub>PWM_D2</sub>    | From PWM falling edge to 90% of $I_{OUT}$ falling edge, $V_{VS}$ = 12 V, $V_{OUT}$ = 6 V, $I_{SET}$ = 100 mA                                                                                                                                 |     | 5   |     | μs   |

| I <sub>OUT</sub> rising edge time              | t <sub>IOUT_E1</sub>   | From 10% of $I_{OUT}$ rising edge to 90% of $I_{OUT}$ rising edge, $V_{VS} = 12$ V, $V_{OUT} = 6$ V, $I_{SET} = 100$ mA                                                                                                                      |     | 3.4 |     | μs   |

| I <sub>OUT</sub> falling edge time             | $t_{IOUT\_E2}$         | From 90% of $I_{OUT}$ falling edge to 10% of $I_{OUT}$ falling edge, $V_{VS} = 12$ V, $V_{OUT} = 6$ V, $I_{SET} = 100$ mA                                                                                                                    |     | 2.8 |     | μs   |

| Device propagation delay                       | t <sub>Prop</sub>      | From VS rising edge to 10% of $I_{OUT}$ rising edge, $V_{VS}$ = 12 V, $V_{OUT}$ = 6 V, $I_{SET}$ = 100 mA (NSL21630)<br>From EN rising edge to 10% of $I_{OUT}$ rising edge, $V_{VS}$ = 12 V, $V_{OUT}$ = 6 V, $I_{SET}$ = 100 mA (NSL21631) |     | 62  |     | μs   |

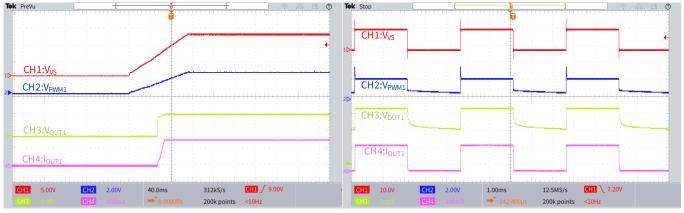

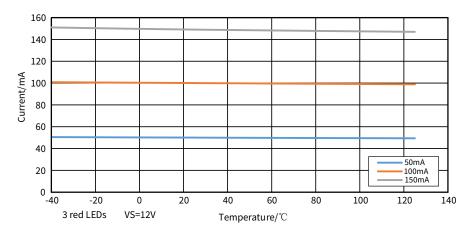

### **6.2. Typical Performance Characteristics**

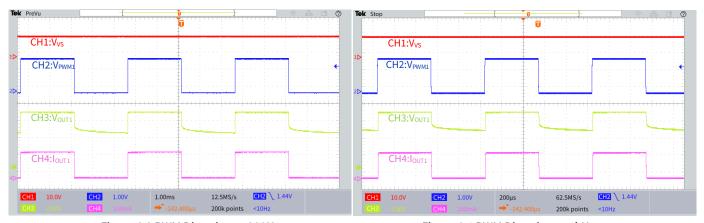

Figure 6.1 Power up

Figure 6.2 Power Supply Dimming at 200Hz

Figure 6.3 PWM Dimming at 200Hz

Figure 6.4 PWM Dimming at 1kHz

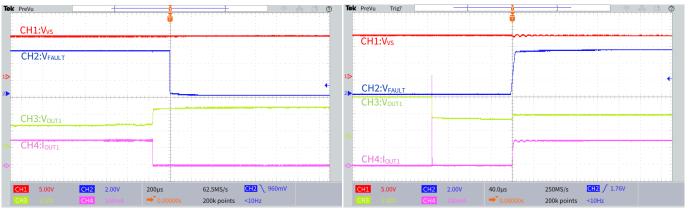

Figure 6.5 Open-Load Protection

Figure 6.6 Open-Load Protection Recovery

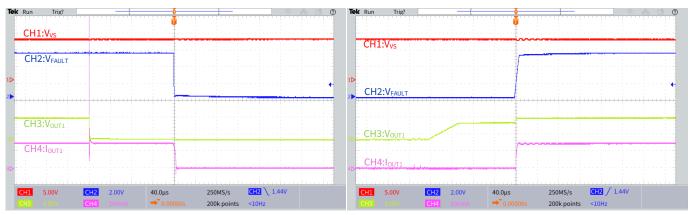

Figure 6.7 Short Protection

Figure 6.8 Short Protection Recovery

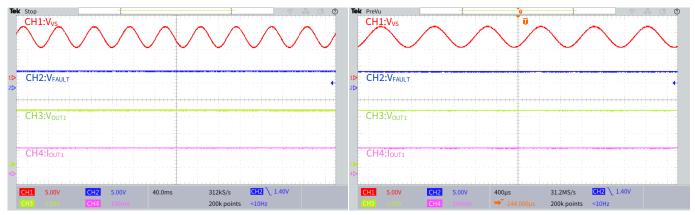

Figure 6.9 Superimposed Alternating Voltage 15Hz

Figure 6.10 Superimposed Alternating Voltage 1kHz

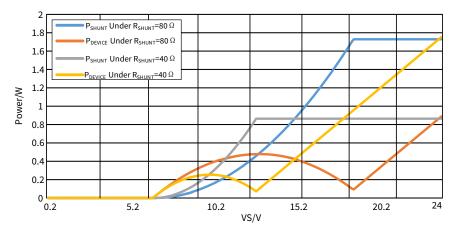

Figure 6.11 Power Dissipation vs Supply Voltage (Iset=150mA)

Figure 6.12 Output Current Distribution vs Supply Voltage

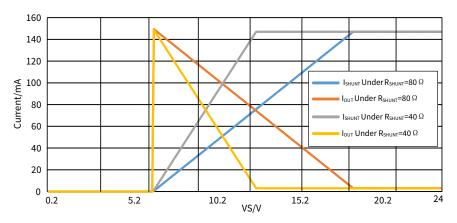

Figure 6.13 Output Current vs Supply Voltage

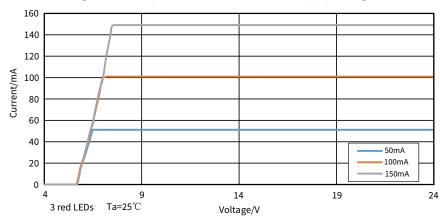

Figure 6.14 Output Current vs Dropout Voltage

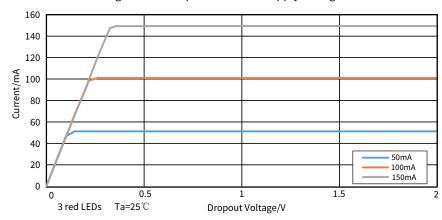

Figure 6.15 Output Current vs Temperature

#### 6.3. Parameter Measurement Information

Figure 6.16 Start up sequence & PWM dimming timing

# 7. Function Description

#### 7.1. Overview

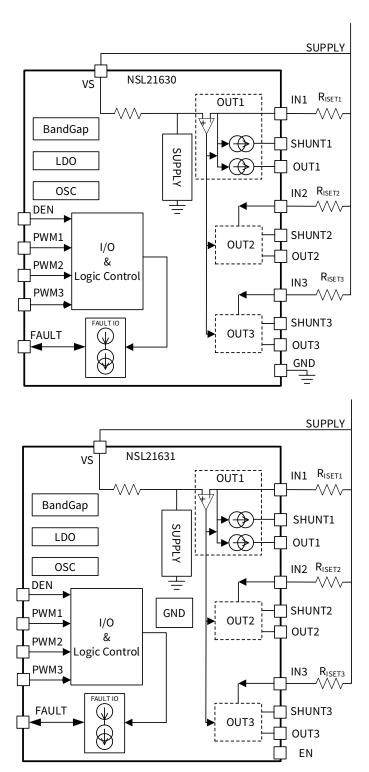

The NSL21630/1 is an automotive three-channel linear LED driver which can be directly powered by automotive batteries. The output current of each channel is independently set by three R<sub>ISET</sub> resistors. By asserting resistors at the SHUNTx pins and dividing channel current between OUTx and SHUNTx outputs, the device includes a unique thermal balancing design to balance thermal between the device and external resistors, thus reducing temperature rising on the device.

The NSL21630/1 device supports brightness control by applying duty cycle on either VS or PWM pins with frequency above 100 Hz. The NSL21630/1 provides full diagnostics to keep the system operating reliably including LED open/short circuit detection and thermal shutdown protection.

### 7.2. System Diagram

Figure 7.1 NSL21630/1 System Diagram

### 7.3. Feature Description

#### 7.3.1 Power supply

#### 7.3.1.1 Power On Reset (POR)

The NSL21630/1 device supports wide range from 5V to 40V of supplied voltage. Besides, an internal power on reset (POR) function is provided. When the power supply pin VS is powered by a source, the POR circuit holds the device in reset mode until V<sub>VS</sub> is higher than Supply voltage POR threshold V<sub>VS,TH1</sub>.

#### 7.3.1.2 On and Off

When the V<sub>VS</sub> is above V<sub>VS,TH1</sub> the NSL21630/1 device starts to output. Otherwise, the device turns off all channels.

#### 7.3.2 Output Current Setting

The NSL21630/1 device is a high-side constant current driver. It controls channel output current through regulating the voltage drop on an external high-side current-sense resistor, R<sub>ISEXT</sub> between VS and INx to V<sub>ISET</sub> independently. When the output current is in regulation, the current value for each channel can be calculated as:

$$I_{CHx} = \frac{V_{ISET}}{R_{ISETy}} \tag{1}$$

Where V<sub>ISET</sub> is 150mV(typical) and x is the number of output channel.

When the total voltage of LED string forward voltage plus required voltage headroom (V<sub>Dropout</sub> + V<sub>ISET</sub>) beyond the supply voltage drops, the NSL21630/1 is not able to deliver enough current output set by the value of R<sub>ISETX</sub>.

#### 7.3.3 Output Current Thermal Balancing

Two current output paths for each channel are provided by NSL21630/1. Current can flow to each LED string through both OUTx pin and SHUNTx pin. The total current output on these two pins is regulated to achieve required current output, and the summed current of OUTx and SHUNTx is equal to the current through RISETX. Thus, it can be calculated as:

$$I_{CHX} = \frac{V_{ISET}}{R_{ISETX}} = I_{OUTX} + I_{SHUNTX}$$

(2)

Where x is the number of output channel.

The output current on both OUTx and SHUNTx output is dynamically adjusted by the integrated current regulation in NSL21630/1 to maintain the stable total current for each channel. In order to reduce the thermal accumulation, the NSL21630/1 always regulates the current output to the SHUNTx pin as much as possible until the SHUNTx current path is saturated. Then OUTx pin provide the rest of required current. As a result, most of the current to LED flows through the SHUNTx pin when the voltage dropout is relatively high between VS and LED total forward voltage. On the contrary, most of the current to LED flows through the OUTx pin when the voltage headroom is relatively low.

Note: the shunt resistor is designed according to real application, and it is calculated with many variables including supply voltage, output voltage, output current. So it is difficult to describe clearly by simple description. A design tool can be provided for customers if any questions occur during application. Please contact us for the design tool.

#### 7.3.4 LED Brightness Dimming

#### 7.3.4.1 PWM Control

The NSL21630/1 supports pulse width modulation (PWM) inputs dimming for LED string. These PWM inputs also can function as enable. The corresponding output current is enabled when the voltage of the PWMx pin is higher than V<sub>Logic\_H</sub>. The output current is disabled with the voltage applied on PWMx pin is lower than V<sub>Logic\_L</sub>. Besides, the average current output for brightness control can be achieved by setting the frequency of applied PWM signal out of visible range of human eyes. It is suggested higher than 100 Hz.

There are three PWM input pins, PWM1, PWM2 and PWM3 in the NSL21630/1 device to control each output channel independently. The outputs OUT1 and SHUNT1 for output channel 1 is controlled by PWM1 input, the outputs OUT2 and SHUNT2 are controlled by PWM2 input, and the outputs OUT3 and SHUNT3 are controlled by PWM3 input.

Figure 7.2 NSL21631 PWM Control LED Brightness Dimming

#### 7.3.4.2 Power Supply Control

The power supply of NSL21630/1 also can control the ON and OFF for all channel output current. When the voltage applied on the VS pin is higher than the LED string forward voltage plus needed voltage headroom (V<sub>Dropout</sub> + V<sub>ISET</sub>), and the voltage of PWM and EN (only for NSL21631) pins is high, the output current is turned ON and well regulated. When the voltage applied on the VS pin drops below UVLO, the output current is turned OFF. With this feature, the power supply voltage in designed pattern can control the output current ON/OFF. The brightness is adjustable if the ON/OFF frequency is fast enough, which is the same as PWM control.

Figure 7.3 NSL21631 Power Supply Control LED Brightness Dimming

To avoid the output current overshoot during turn-on phase, it is suggested to enable the PWM through resistor as below connection:

$$V_{VS\_PWM\_RISING} = V_{Logic\_H} \times \left(1 + \frac{R_1}{R_2}\right)$$

(3)

$$V_{VS PWM RISING} \ge V_{LED FWD TOT} + V_{Dropout} + V_{ISET}$$

(4)

To avoid the false open-load detection due to low-dropout region operation during turn-on/off phase, it is suggested to enable the DEN through resistor as below connection:

$$V_{VS\_DEN\_FALLING} = V_{Logic\_L} \times \left(1 + \frac{R_3}{R_4}\right)$$

(5)

$$V_{VS\_DEN\_FALLING} \ge V_{LED\_FWD\_TOT} + V_{OPEN,TH2} + V_{ISET}$$

(6)

Where V<sub>Logic\_H</sub> is 1.258V (maximum), V<sub>Logic\_L</sub> is 1.066V (minimum)

#### 7.3.5 Protections and Diagnostics

#### 7.3.5.1 Open-Load Detection

The device has LED open-load detection. The LED open-load detection monitors the output voltage when the current output is enabled. The LED open-load detection is only enabled when DEN is HIGH. A short-to-battery fault is also detected and recognized as an LED open-load fault. Once a LED open-load failure is detected, the device turns off the faulty channel and retries automatically, regardless of the state of the PWM input. When the retry mechanism detects the removal of the LED open-load fault, the device resumes to normal operation.

When the device operates in normal mode with PWM and EN (only for NSL21631) voltage is high, the NSL21630/1 monitors dropout-voltage differences between the VS and OUTx pins for each LED channel. The voltage difference  $V_{VS}-V_{OUTx}$  is compared with the internal reference voltage  $V_{OPEN,TH2}$  to detect LED open-circuit incident. When  $V_{OUTx}$  rises causing  $V_{VS}-V_{OUTx}$  less than the  $V_{OPEN,TH2}$  voltage and lasts longer the deglitch time of  $t_{O/S\_Deg}$ , the device asserts an open-load fault. When DEN input is logic High,once a LED open-load failure is detected, the internal constant-current sink pulls down the FAULT pin voltage. The device shuts down the output current regulation for the faulty channel. However, the device sources a small current  $t_{O/S\_Retry}$  from Vs to OUT. The device resumes normal operation and releases the FAULT pin once the fault condition is removed.

#### 7.3.5.2 Short-to-GND Detection

In order to ensure the safety of the device and the total system, LED short-to-GND detection is integrated in NSL21630/1. This function is achieved by monitoring the output voltage when the output current is enabled, and regardless of the state of the DEN input. Once a short-to-GND LED failure is detected, the device turns off the faulty channel and retries automatically, regardless of the state of the PWM input. When the retry mechanism detects the removal of the LED short-to-GND fault, the device resumes to normal operation.

The device monitors the  $V_{OUTx}$  voltage and  $V_{SHUNTx}$  voltage of each channel and compares it with the internal reference voltage to detect a short-to-GND failure. When  $V_{OUTx}$  or  $V_{SHUNTx}$  voltage falls below  $V_{SHORT,TH2}$  longer than the deglitch time of  $t_{O/S\_Deg}$ , the device asserts the short-to-GND fault, then pulls low the FAULT pin to assert the fault happen. Once the device has asserted a short-to-GND fault, the device turns off the faulty output channel and retries automatically with a small current,  $I_{O/S\_Retry}$  from VS to OUT to pull up the LED loads continuously. Once auto-retry detects output voltage rising above  $V_{SHORT,TH1}$ , it clears the short-to-GND fault and resumes to normal operation. Please refer to the Fault table 7.1 for details.

#### 7.3.5.3 Thermal Shutdown

The junction temperature is monitored every time by the NSL21630/1 device. The output current will be shutdown if the junction temperature reaches thermal shutdown threshold (T<sub>SD</sub>). Note that, there is a thermal hysteresis exits, which means only the junction temperature falls below T<sub>SD</sub>-T<sub>HYST</sub>, then the device recovers to normal mode. The FAULT pin is pulled low during thermal shutdown.

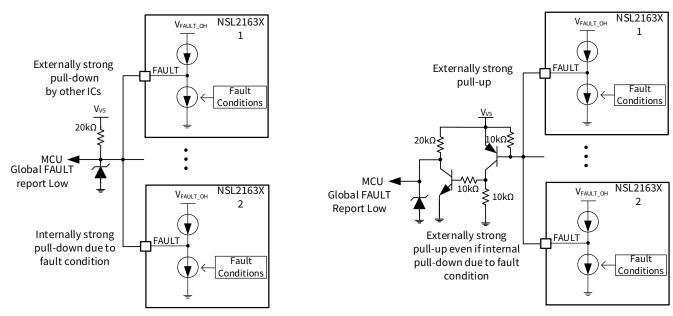

#### 7.3.5.4 Fault Bus

The state of FAULT pin represents the current state of the device. When any fault scenario occurs, the FAULT pin will be strongly pulled low by the internal pulldown current sink, IFAULT\_PD. And the device will report the fault alarm. If no fault scenario occurs, it means the device is operating in normal mode, and the FAULT pin is weakly pulled up by an internal pullup current source, IFAULT\_PU. At the same time, the device also monitors the FAULT pin voltage internally. If the FAULT pin is pulled down below VFAULT\_IL by external current sink, the current output is turned off even though there is no fault detected on owned outputs.

For multiple NSL21630/1 devices application, one is able to construct a FAULT bus by tying FAULT pins from other devices to achieve fault sharing function as shown in Figure 7.4, It means one device detects any fault and pull down the FAULT pin, then the FAULT bus will turn off all the device in the bus. Another situation is that one device detects any fault and turn off its own current output, but the others will operate normally by connecting all the FAULT pins to the base of an external PNP transistor as illustrated in Figure 7.5

Figure 7.4 All off if one fails application

Figure 7.5 Others remain on if one fails application

EN **Fault Bus Detection PWMx** DEN **Deglitch FAULT Action Device Action Fault Type** Recovery **Status** Mechanism Input **Time** Input Input Device turns failed **FAULT** internal channel off and Open-load or Auto- $V_{VS} - V_{OUTx} < V_{OPEN,TH2}$ Н Н Н pulldown retries with to/S Deg Short to battery recovery current, I<sub>O/S\_Retry</sub>, ignoring the PWM input. IFAULT PD **FAULT** Device turns failed internal channel off and **FAULT** V<sub>OUTx</sub> < V<sub>SHORT,TH2</sub> OR Autonot Short to ground Н Н  $t_{\text{O/S\_Deg}}$ pulldown retries with HIGH V<sub>SHUNTx</sub> <V<sub>SHORT,TH2</sub> care recovery current,  $I_{\text{O/S\_Retry}}\text{, ignoring}$ the PWM input.  $I_{\text{FAULT\_PD}}$ **FAULT** internal Thermal Device turns all not not Auto- $T_J > T_{SD}$ Н 120us pulldown shutdown channels off care care recovery current,  $I_{FAULT\_PD}$ Fault detected Device turns all channels off and keeps auto-retry on failed channels **FAULT** LOW No Fault Device turns all channels off

Table 7.1 Fault table

### 7.4. Device Operation Mode

#### 7.4.1 Normal Operation

With the supplied voltage ≥4.8V, the NSL21630/1 operate in normal mode. The LED string is derived in constant-current with enough voltage drop across Vs and OUT.

#### 7.4.2 Undervoltage Lockout(UVLO)

All the functions of NSL21630/1 are disabled in this mode. If Vvs >Vvs,TH1, the device will quit this mode.

#### 7.4.3 Low Dropout Operation

When the voltage supply is low and the voltage difference between input and output is less than the open-load detection threshold, the device will report an open-load fault. So it is suggested only enabling the open-load detection when the voltage across Vs and out is higher than the maximum voltage of open-load threshold to avoid a false detection.

#### 7.4.4 Fault Operation

The FAULT pin will be pulled down with a constant current if any fault is detected. Then the device operates into a fault mode and consumes a fault current of IQ\_FAULT.

# 8. Application

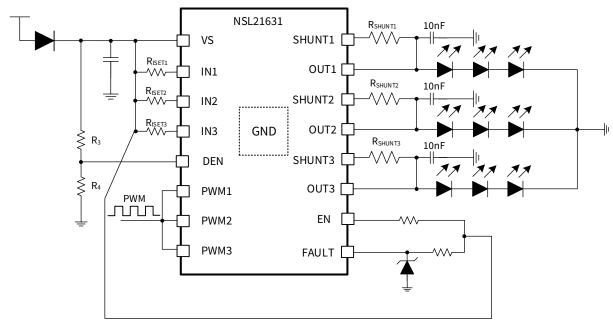

The fellow parts are not the component specification. The typical application in the fellow parts only helping customers to understand the functions of NSL21630/1, and it also able to provide a design guideline for some applications. By the way, the examples are provided based on NSL21631. For NSL21630, the only difference is the EN pin, and the examples are also suitable by neglecting the EN pin. Customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

### 8.1 Typical Application Circuit

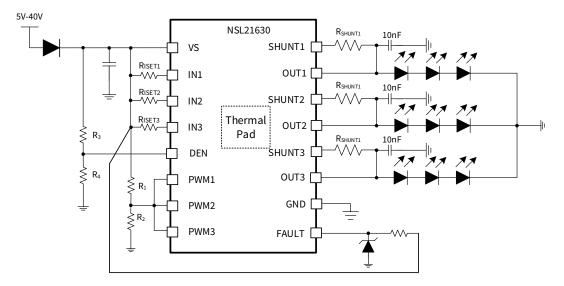

#### 8.1.1 Simple Application without MCU

The NSL21630/1 devices can be utilized without external MCU for automotive rear lamp including turn indicator, tail, fog, stop and so on.

Figure 8.1. NSL21630/1 Simple Application Without MCU

#### 8.1.1.1. Design Information

The voltage supply for VS is from 9V to 16V, and the dimming method is through power supply on and off. A total 3 strings with 3 LEDs in each string are drived by a NSL21630/1 device. The LED forward voltage drop is between 1.9V(V<sub>LED\_min</sub>) to 2.5V(V<sub>LED\_max</sub>). The current flow of every LED is 130mA.

#### 8.1.1.2. Design Procedure

Step 1: calculate RISETX using the equation below

$$R_{ISETX} = \frac{V_{ISET}}{I_{IFDX}} \tag{7}$$

Where V<sub>ISET</sub>=150mV, I<sub>LEDX</sub>=130mA, X is the channel number.

Due to the required output current for each LED,  $R_{ISETX} = 1.15\Omega$ .

**Step 2**: Calculate the current of  $I_{OUTX}$  and  $I_{SHUNTX}$ , and the shunt resistor  $R_{SHUNTX}$  can be obtained by using Equation 8. The shunt resistor directly decides the current distribution for  $I_{OUTX}$  path and  $I_{SHUNTX}$  path. In typical supply voltage application, the current shunt resistor is suggested to consume 50% of the total output current.

$$R_{SHUNTX} = \frac{V_{VS} - V_{OUTX}}{I_{OUTX} \times 0.5}$$

(8)

Where  $V_{VS}$ =12V(typical),  $I_{LEDX}$ =130mA, X is the channel number.

The value of shunt resistor for all three channel is calculated as  $85.4\Omega$ , when the output voltage is selected as  $2.15\times3=6.45V$ .

**Step 3**: Design the voltage divider resistor value of R<sub>3</sub> and R<sub>4</sub> on DEN pin after design the threshold voltage of supply to enable the open-load diagnostics.

Note that, the open-load fault cannot be detected in low dropout operation to avoid unexpected turn off, so headroom between voltage Vs and out must be considered. It means the device must disable open-load detection when the voltage supply is below the maximum LED string forward voltage plus open-load threshold  $V_{OPEN,TH2}$  and  $V_{ISET}$ . The voltage divider  $R_3$  and  $R_4$  can be obtained as Equation 9.

$$R_3 = \left(\frac{V_{OPEN,TH2} + V_{ISET} + V_{OUT}}{V_{IOPIC}} - 1\right) \times R_4 \tag{9}$$

Where  $V_{OPEN,th2} = 390 \text{mV} (\text{maximum})$ ,  $V_{ISET} = 150 \text{mV}$ ,  $V_{Logic\_L} = 1.066 \text{V} (\text{minimum})$ ,  $R_4 = 10 \text{k} \Omega (\text{recommended})$ .

When the maximum LED string forward voltage is 2.5V×3=7.5V, R<sub>3</sub>=65.4kΩ is obtained.

**Step 4**: Calculate the divider resistor of  $R_1$  and  $R_2$  of PWM pin to turn on and off each channel of LED, after the threshold voltage supply is determined.

In order to ensure all the LEDs is operating in normal mode, each LED should be turn off if the voltage supply is lower than LED minimum required forward voltage plus voltage dropout between Vs and OUTX. The minimum forward voltage of LED string is calculated as  $1.9V \times 3=5.7V$ . Thus, the divider resistor  $R_1$  and  $R_2$  can be calculated by Equation 10.

$$R_1 = \left(\frac{V_{Dropout} + V_{ISET} + V_{OUT}}{V_{Logic\_H}} - 1\right) \times R_2$$

(10)

Where  $V_{Dropout} = 240 \text{mV} (typical)$ ,  $V_{ISET} = 150 \text{mV}$ ,  $V_{Logic\_H} = 1.258 \text{V} (maximum)$ ,  $R_2 = 10 \text{k}\Omega (recommended)$ .

According to Equation 10,  $R_1$  is 38.4k $\Omega$  when the minimum voltage of OUTX is 5.7V.

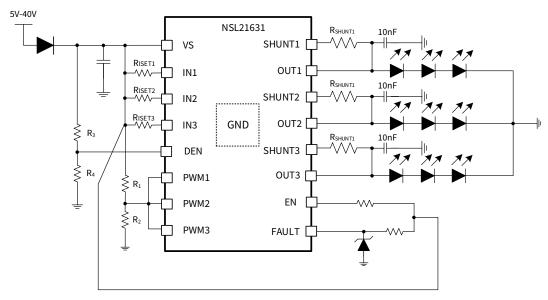

#### 8.1.2 Application with MCU

The NSL21630/1 devices support three channels independently dimming control by PWM input signals which providing by external MCU. The PWM input pins should be connected to MCU out pins to achieve more complex application like sequential turn indicator.

Figure 8.2 NSL21630/1 Simple Application With MCU

### 8.1.2.1 Design Information

The voltage supply for VS is from 9V to 16V, and the dimming method is through three PWM input pins. A total 3 strings with 3 LEDs in each string are drived by a NSL21630/1 device. The LED forward voltage drop is between 1.9V(V<sub>LED\_min</sub>) to 2.5V(V<sub>LED\_max</sub>). The current flow of every LED is 130mA. External MCU is adopted to give three PWM control signals for PWM dimming control as shown in Figure 8.2

#### 8.1.2.2 Design Procedure

Step 1: calculate RISETX using the equation below

$$R_{ISETX} = \frac{V_{ISET}}{I_{LEDX}} \tag{11}$$

Where V<sub>ISET</sub>=150mV(typical), I<sub>LEDX</sub>=130mA, X is the channel number.

Due to the required output current for each LED,  $R_{ISETX}$  =1.15 $\Omega$ .

**Step 2**: Calculate the current of I<sub>OUTX</sub> and I<sub>SHUNTX</sub>, and the shunt resistor R<sub>SHUNTX</sub> can be obtained by using Equation 12. The shunt resistor directly decides the current distribution for I<sub>OUTX</sub> path and I<sub>SHUNTX</sub> path. In typical supply voltage application, the current shunt resistor is suggested to consume 50% of the total output current.

$$R_{SHUNTX} = \frac{V_{VS} - V_{OUTX}}{I_{OUTX} \times 0.5}$$

(12)

Where V<sub>VS</sub>=12V(typical), I<sub>LED</sub>=130mA, X is the channel number.

The value of shunt resistor for all three channel is calculated as  $83.1\Omega$ , when the output voltage is selected as  $2.2\times3=6.6V$ .

**Step 3**: Design the voltage divider resistor value of R<sub>3</sub> and R<sub>4</sub> on DEN pin after design the threshold voltage of supply to enable the open-load diagnostics.

Note that, the open-load fault cannot be detected in low dropout operation to avoid unexpected turn off, so headroom between voltage supply and out must be considered. It means the device must disable open-load detection when the voltage supply is below the maximum LED string forward voltage plus open-load threshold  $V_{OPEN,TH2}$  and  $V_{ISET}$ . The voltage divider  $R_1$  and  $R_2$  can be obtained as Equation 13.

$$R_3 = \left(\frac{V_{OPEN,TH2} + V_{ISET} + V_{OUT}}{V_{Logic\ L}} - 1\right) \times R_4 \tag{13}$$

Where  $V_{OPEN,TH2}$  = 390mV(maximum),  $V_{ISET}$  = 150mV,  $V_{Logic\_L}$  = 1.066V(minimum),  $R_4$ =10k $\Omega$ (recommended).

When the maximum LED string forward voltage is 2.5V×3=7.5V, R<sub>3</sub>=65.46kΩ is obtained.

### 9. Layout

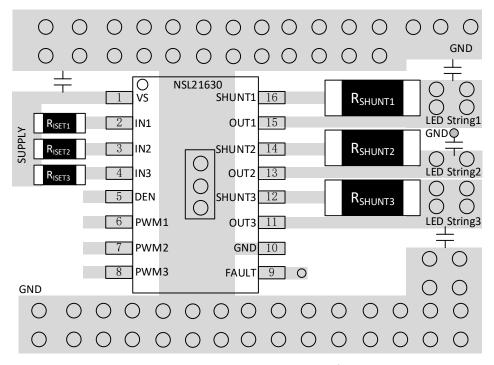

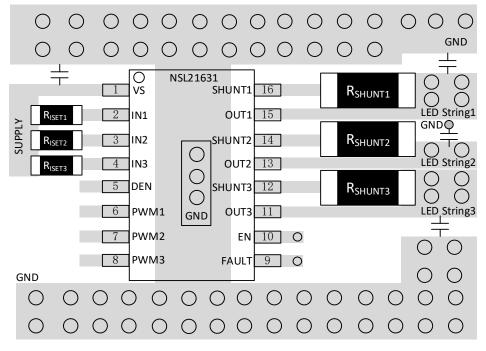

### 9.1. Layout Guidelines

The thermal dissipation must be considered for NSL21630/1 layout.

- 1: Thermal dissipation area in both top and bottom layers of PCB should be as larger as possible. The thermal pad in the bottom of the device must be reliable welding, and copper pouring in opposite PCB layer or inner layers must be connected to thermal pad directly through multiple thermal vias.

- 2: The shunt resistors should far away from the device with more than 2cm distance. The large copper pouring area is also required surrounding the R<sub>SHUNT</sub> resistors for helping thermal dissipating. Other heat source components should be placed away from the device and shunt resistor.

- 3: NSL21631 EP pad are IC GND pad, and NSL21630 EP pad are thermal pad. In order to ensure the device good GND connection and heat dissipation on the PCB board. We recommend that the PCB stencil thickness is 0.15mm, The EP pads adopted fully opening window to ensure good welding.

Another consideration for the PCB layout is noise immunity.

- 1: Place decoupling capacitors for VS and out pins as close as possible to the pins.

- 2: If possible, the GND pin should be connected the housing (metal) with shortest track.

- 3: The long signal trace is not recommended in the PCB.

- 4: If possible, the device should be away from high power device with high frequency.

### 9.2. Layout Example

Figure 9.1. Example Layout Diagram for NSL21630

Figure 9.2. Example Layout Diagram for NSL21631

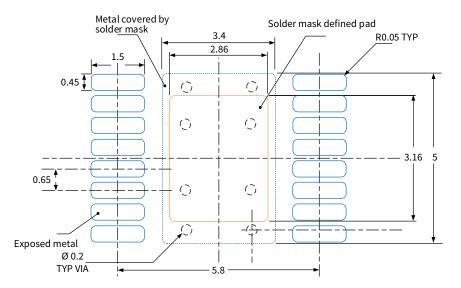

### 9.3. Recommended Footprint

Figure 9.3. Recommended Land Pattern

#### Notes:

- 1. Above recommended footprint is based on 0.15mm thick stencil.

- 2. All dimensions are in millimeters.

- 3. Drawing is not to scale.

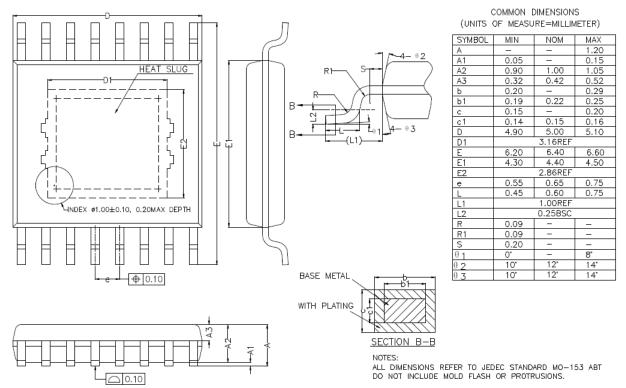

# 10. Package Information

Figure 10.1 HTSSOP-16 Package Shape and Dimension in millimeters

### 11. Order Information

| Part Number     | Output<br>Channel | Output Current         | Thermal Pad               | Thermal<br>Balance | EN  | MSL | MPQ         |

|-----------------|-------------------|------------------------|---------------------------|--------------------|-----|-----|-------------|

| NSL21610-Q1HMSR | 1                 | 450mA(MAX)             | GND                       | Yes                | Yes | 3   | 2500ea/reel |

| NSL21611-Q1HMSR | 1                 | 300mA(MAX)             | Suggest connect<br>to GND | No                 | Yes | 3   | 2500ea/reel |

| NSL21630-Q1HTPR | 3                 | 200mA/per channel(MAX) | Suggest connect<br>to GND | Yes                | No  | 3   | 4000ea/reel |

| NSL21631-Q1HTPR | 3                 | 200mA/per channel(MAX) | GND                       | Yes                | Yes | 3   | 4000ea/reel |

# 12. Documentation Support

| Part Number       | Datasheet  | Technical Documents |

|-------------------|------------|---------------------|

| NSL21630/1-Q1HTPR | Click here | /                   |

| NSL21610/1-Q1HMSR | Click here | /                   |

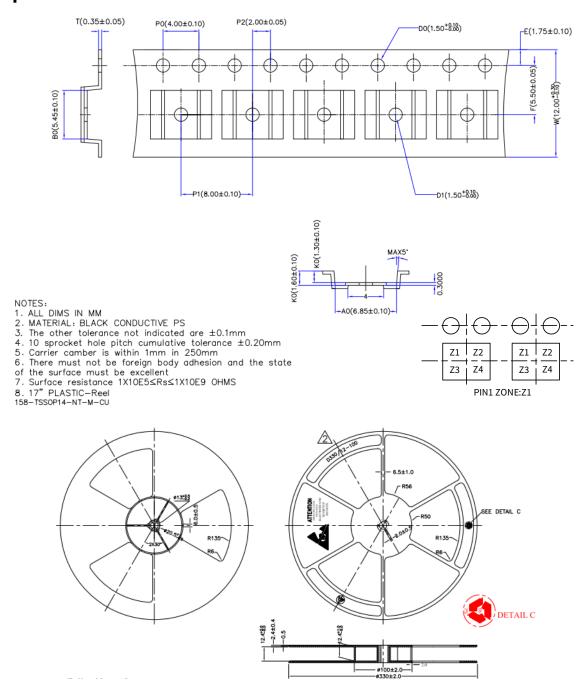

# 13. Tape and Reel Information

Figure 13.1 Tape and Reel Information

Note: 4000ea/reel.

NSL21630/1

Datasheet (EN) 1.0

# 14. Revision history

| Revision | Description                                        | Date    |

|----------|----------------------------------------------------|---------|

| 1.0      | Change from Advance Information to Production Data | 2022/08 |

#### IMPORTANT NOTICE

The information given in this document (the "Document") shall in no event be regarded as any warranty or authorization of, express or implied, including but not limited to accuracy, completeness, merchantability, fitness for a particular purpose or infringement of any third party's intellectual property rights.

Users of this Document shall be solely responsible for the use of NOVOSENSE's products and applications, and for the safety thereof. Users shall comply with all laws, regulations and requirements related to NOVOSENSE's products and applications, although information or support related to any application may still be provided by NOVOSENSE.

This Document is provided on an "AS IS" basis, and is intended only for skilled developers designing with NOVOSENSE' products. NOVOSENSE reserves the rights to make corrections, modifications, enhancements, improvements or other changes to the products and services provided without notice. NOVOSENSE authorizes users to use this Document exclusively for the development of relevant applications or systems designed to integrate NOVOSENSE's products. No license to any intellectual property rights of NOVOSENSE is granted by implication or otherwise. Using this Document for any other purpose, or any unauthorized reproduction or display of this Document is strictly prohibited. In no event shall NOVOSENSE be liable for any claims, damages, costs, losses or liabilities arising out of or in connection with this Document or the use of this Document.

For further information on applications, products and technologies, please contact NOVOSENSE (www.novosns.com).

Suzhou NOVOSENSE Microelectronics Co., Ltd