# NCA1021S LIN transceiver with multiple modes

Datasheet (EN) 1.1

### **Product Overview**

The NCA1021S is a LIN (Local Interconnect Network) transceiver with a low-power mode and multiple wakeup methods. It supports up to 20 kbps for sending and receiving communication and is compliant with LIN 2.0, LIN 2.1, LIN 2.2, LIN 2.2A, SAE J2602 and ISO 17987-4: 2016 (12V LIN systems).

In sleep mode, the power consumption of NCA1021S is extremely low. Support remote wake-up and local wakeup via LIN bus, pin WAKE\_N and pin SLP\_N. The device can also use the INH output pin as a sign to control the working state of other devices in the local system, such as the voltage regulator, to achieve low power operation of the system.

The NCA1021S converts the signal received by TXD into a LIN bus signal through waveform shaping and slew rate adjustment to reduce electromagnetic emission (EME). TXD has a fault time-out protection function to prevent the LIN bus from being occupied.

### **Key Features**

- Compliant to LIN 2.0, LIN 2.1, LIN 2.2, LIN 2.2A, SAE J2602 and ISO 17987–4 standard

- Very low electromagnetic emission (EME)

- High electromagnetic immunity (EMI)

- Support for 12 V applications

- Input levels compatible with 3.3 V and 5 V devices

- Bus fault protection of -40 V to +40 V

- Wake-up source recognition (local or remote)

- Integrated LIN pull-up resistor

- Transmit data (TXD) dominant time-out function

- K-line compatible

- AEC-Q100 qualified for automotive applications (Grade 1)

- Over temperature protection

- Date rate: up to 20 kbps

- Operation temperature range: -40  $^\circ\!\mathrm{C}$  ~125  $^\circ\!\mathrm{C}$

- RoHS compliance

- Available packages:

SOP8

DFN8

### Applications

- Body sensor and module control

- Car steering wheel and instrument cluster

- Powertrain system and electric engine

### **Device Information**

| Part Number    | Package | Body Size       |

|----------------|---------|-----------------|

| NCA1021S-Q1SPR | SOP8    | 4.90mm × 3.90mm |

| NCA1021S-Q1DNR | DFN8    | 3.00mm × 3.00mm |

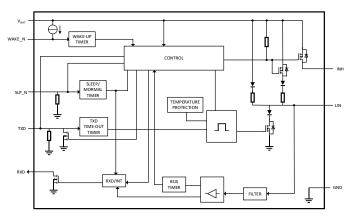

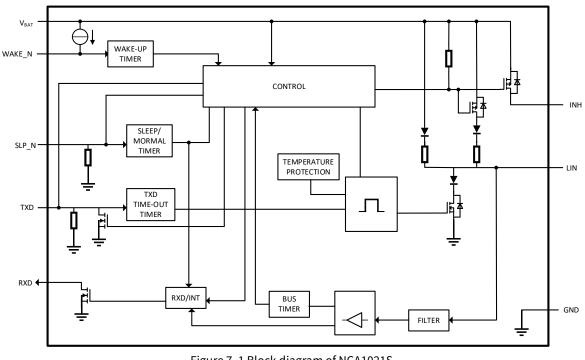

### **Function Block Diagram**

Figure 1. NCA1021S block diagram

### INDEX

| 1. PIN CONFIGURATION AND FUNCTIONS     | 3 |

|----------------------------------------|---|

| 2. ABSOLUTE MAXIMUM RATINGS            | 4 |

| 3. ESD RATINGS                         | 4 |

| 4. RECOMMENDED OPERATING CONDITIONS    | 5 |

| 5. THERMAL CHARACTERISTICS             | 5 |

| 6. SPECIFICATIONS                      | 5 |

| 6.1. ELECTRICAL CHARACTERISTICS        |   |

| 6.2. Switching Characteristics         |   |

| 6.3. PARAMETER MEASUREMENT INFORMATION |   |

| 7. FUNCTION DESCRIPTION                |   |

| 7.1. Overview                          |   |

| 7.2. Device Functional Modes           |   |

| 7.2.1 Power-on mode                    |   |

| 7.2.2 Normal mode                      |   |

| 7.2.3 Steep mode<br>7.2.4 Standby mode |   |

| 7.3. PIN CHARACTERISTICS               |   |

| 7.3.1 RXD                              |   |

| 7.3.2 SLP_N                            |   |

| 7.3.3 WAKE_N                           |   |

| 7.3.4 TXD                              |   |

| 7.3.5 LIN                              |   |

| 7.3.6 V <sub>BAT</sub>                 |   |

| 7.3.7 INH                              |   |

| 7.4. TXD DOMINANT TIME-OUT FUNCTION    |   |

| 7.5. FAIL-SAFE FEATURES                |   |

| 8. APPLICATION NOTE                    |   |

| 8.1. TYPICAL APPLICATION               |   |

| 9. PACKAGE INFORMATION                 |   |

| 10. ORDER INFORMATION                  |   |

| 11. TAPE AND REEL INFORMATION          |   |

| 12. REVISION HISTORY                   |   |

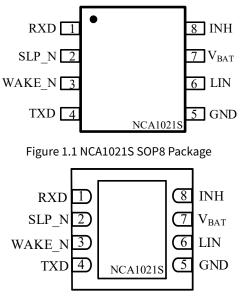

### **1. Pin Configuration and Functions**

Figure 1.2 NCA1021S DFN8 Package

#### Table1.1 NCA1021S Pin Configuration and Description

| NCA1021S PIN NO. | SYMBOL           | FUNCTION                                                                                                                                                     |

|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | RXD              | Receive data output (open-drain).<br>In standby mode, the RXD pin is driven low to indicate a wake-up request.                                               |

| 2                | SLP_N            | Sleep control input (active low) integrated pull down.<br>When SLP_N is high the device is in normal mode,<br>When SLP_N is low the device is in sleep mode. |

| 3                | WAKE_N           | Local wake-up input (active low), negative edge triggered, high voltage.                                                                                     |

| 4                | TXD              | Transmit data input, integrated pull down, active low output after a local wake-up event.                                                                    |

| 5                | GND              | Ground                                                                                                                                                       |

| 6                | LIN              | LIN bus line, input/output                                                                                                                                   |

| 7                | V <sub>BAT</sub> | Battery supply voltage, high voltage.                                                                                                                        |

| 8                | INH              | Battery related inhibit output for controlling an external voltage regulator,<br>high voltage. Only floating in sleep mode, the rest is high.                |

### 2. Absolute Maximum Ratings

| Parameters                    | Symbol              | Min  | Тур | Мах                    | Unit | Comments                                                                                       |

|-------------------------------|---------------------|------|-----|------------------------|------|------------------------------------------------------------------------------------------------|

| Battery supply voltage        | V <sub>BAT</sub>    | -0.3 |     | 40                     | V    | With respect to GND                                                                            |

| Voltage on pin TXD            | V <sub>TXD</sub>    | -0.3 |     | 6                      | V    | ITXD no limitation                                                                             |

| Voltage on pin 1XD            | <b>V</b> TXD        | -0.3 |     | 7                      | V    | Ι <sub>τχD</sub> < 500 μΑ                                                                      |

| Veltage on pin BYD            | V <sub>RXD</sub>    | -0.3 |     | 6                      | V    | I <sub>RXD</sub> no limitation                                                                 |

| Voltage on pin RXD            | <b>V</b> RXD        | -0.3 |     | 7                      | V    | I <sub>RXD</sub> < 500 μA                                                                      |

| Voltage on pin SLD N          | V                   | -0.3 |     | 6                      | V    | $I_{SLP_N}$ no limitation                                                                      |

| Voltage on pin SLP_N          | $V_{SLP_N}$         | -0.3 |     | 7                      | V    | I <sub>SLP_N</sub> < 500 μA                                                                    |

| Voltage on pin LIN            | V <sub>LIN</sub>    | -40  |     | 40                     | V    | Limiting value with respect to GND, VBAT and VWAKE_N                                           |

| Voltage on pin WAKE_N         | $V_{WAKE_N}$        | -0.3 |     | 40                     | V    |                                                                                                |

| Current on pin WAKE_N         | Iwake_n             | -15  |     |                        | mA   | Only relevant if V <sub>WAKE_N</sub> < V <sub>GND</sub> -0.3<br>current will flow into pin GND |

| Voltage on pin INH            | V <sub>INH</sub>    | -0.3 |     | V <sub>BAT</sub> + 0.3 | V    |                                                                                                |

| Output current on pin INH     | I <sub>O(INH)</sub> | -50  |     | 15                     | mA   |                                                                                                |

| Operation ambient temperature | Ta                  | -40  |     | 125                    |      |                                                                                                |

| Virtual junction temperature  | T <sub>vj</sub>     | -40  |     | 150                    | °C   |                                                                                                |

| Storage temperature           | T <sub>stg</sub>    | -55  |     | 150                    |      |                                                                                                |

Current into device pins is defined as positive. Current out of device pins is defined as negative.

# 3. ESD ratings

| Symbol    | Ratings                                       | Value | Unit |

|-----------|-----------------------------------------------|-------|------|

|           | Human body model (JESD22/A114) - 100pF, 1.5kΩ |       |      |

| Vesd-hbm1 | • Pins LIN and V <sub>BAT</sub>               | ±8.0  | kV   |

| Vesd-hbm2 | • Other pins                                  | ±7.0  |      |

|           | Charged device model (JESD22/C101):           |       | kV   |

| Vesd-cdm1 | All pins                                      | ±1.5  | ĸ۷   |

### 4. Recommended Operating Conditions

| Parameters                   | Symbol           | Min  | Тур | Мах | Unit |

|------------------------------|------------------|------|-----|-----|------|

| Battery supply voltage       | V <sub>BAT</sub> | 5.5  |     | 27  | V    |

| LIN Bus input voltage        | V <sub>LIN</sub> | 0    |     | 27  | V    |

| TXD high-level input voltage | VIH              | 2    |     | 7   | V    |

| TXD low-level input voltage  | VIL              | -0.3 |     | 0.8 | V    |

### 5. Thermal Characteristics

| Parameters                                | Symbol                | SOP8  | DFN8 | Unit |

|-------------------------------------------|-----------------------|-------|------|------|

| Junction-to-air thermal resistance        | $\theta_{JA}$         | 125.3 | 53.3 | °C/W |

| Junction-to-case (top) thermal resistance | $\theta_{JC \ (top)}$ | 65.4  | 60   | °C/W |

| Junction-to-board thermal resistance      | θ <sub>ЈВ</sub>       | 68.7  | 25.6 | °C/W |

### 6. Specifications

### **6.1.Electrical Characteristics**

$(V_{BAT} = 5.5 V \text{ to } 27 V, T_{vj} = -40 \degree C \text{ to } 150 \degree C.$  Unless otherwise noted, typical values are at  $V_{BAT} = 12 V, T_a = 25\degree C$ ).

| Parameters             | Symbol                              | Min | Тур | Мах  | Unit | Comments                                                                                                                 |

|------------------------|-------------------------------------|-----|-----|------|------|--------------------------------------------------------------------------------------------------------------------------|

|                        |                                     |     |     | 20   | μΑ   | Sleep mode, $V_{LIN} = V_{BAT} = V_{WAKE_N}$ ,<br>$V_{TXD} = V_{SLP_N} = 0 V$                                            |

|                        |                                     |     |     | 150  | μΑ   | Standby mode, bus recessive<br>$V_{INH} = V_{LIN} = V_{WAKE_N} = V_{BAT}, V_{TXD} = V_{SLP_N} = 0 V$                     |

| Battery supply current | Ibat                                |     |     | 1200 | μΑ   | Standby mode, bus dominant<br>$V_{BAT} = V_{INH} = V_{WAKE_N} = 12 V, V_{LIN} = 0 V$<br>$V_{TXD} = 0 V, V_{SLP_N} = 0 V$ |

|                        |                                     |     |     | 1600 | μΑ   | Normal mode, bus recessive<br>$V_{INH} = V_{LIN} = V_{WAKE_N} = V_{BAT}$<br>$V_{TXD} = 5 V, V_{SLP_N} = 5 V$             |

|                        |                                     |     |     | 4    | mA   | Normal mode, bus dominant<br>$V_{BAT} = V_{INH} = V_{WAKE_N} = 12 V$<br>$V_{TXD} = 0V, V_{SLP_N} = 5 V$                  |

| Power on reset         | $V_{\text{th}(\text{POR})\text{L}}$ | 1.6 | 3.1 | 3.9  | v    | Low-level power-on reset threshold voltage                                                                               |

|                        | $V_{th(POR)H}$                      | 2.3 | 3.4 | 4.3  | v    | High-level power-on reset threshold voltage                                                                              |

# Datasheet (EN) 1.1

| Parameters                           | Symbol                         | Min                 | Тур | Мах                    | Unit | Comments                                                                                                                          |

|--------------------------------------|--------------------------------|---------------------|-----|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                      | $V_{hys(POR)}$                 | 0.01                | 0.3 | 1                      | V    | Power-on reset hysteresis voltage                                                                                                 |

|                                      | $V_{th(VBATL)L}$               | 3.9                 | 4.4 | 4.7                    | V    | Low-level V <sub>BAT</sub> LOW threshold voltage                                                                                  |

|                                      | $V_{\text{th(VBATL)H}}$        | 4.2                 | 4.7 | 4.9                    | V    | High-level VBAT LOW threshold voltage                                                                                             |

|                                      | $V_{\text{hys}(\text{VBATL})}$ | 0.01                | 0.3 | 1                      | V    | V <sub>BAT</sub> LOW hysteresis voltage                                                                                           |

| TXD                                  |                                |                     |     |                        | •    |                                                                                                                                   |

| High-level input voltage             | VIH                            | 2                   |     | 7                      | V    |                                                                                                                                   |

| Low-level input voltage              | VIL                            | -0.3                |     | 0.8                    | V    |                                                                                                                                   |

| Hysteresis voltage                   | $V_{\text{hys}}$               |                     | 160 |                        | mV   | Guaranteed by design                                                                                                              |

| Low-level input current              | Iιι                            | -5                  |     | 5                      | μA   |                                                                                                                                   |

| Output low current                   | loL                            | 1.5                 |     |                        | mA   | Local wake-up request, standby mode,<br>V <sub>WAKE_N</sub> = 0 V, V <sub>LIN</sub> = V <sub>BAT</sub> , V <sub>TXD</sub> = 0.4 V |

| Pull-down resistance on<br>pin TXD   | Rpd(txd)                       | 140                 |     | 1200                   | kΩ   |                                                                                                                                   |

| SLP_N                                |                                |                     |     |                        |      |                                                                                                                                   |

| High-level input voltage             | VIH                            | 2                   |     | 7                      | V    |                                                                                                                                   |

| Low-level input voltage              | VIL                            | -0.3                |     | 0.8                    | V    |                                                                                                                                   |

| Hysteresis Voltage                   | $V_{\text{hys}}$               |                     | 120 |                        | mV   | Guaranteed by design                                                                                                              |

| Low-Level Input Current              | lı.                            | -5                  |     | 5                      | μΑ   | $V_{SLP_N} = 0 V$                                                                                                                 |

| Pull-down resistance on<br>pin SLP_N | Rpd(slp_n)                     | 140                 |     | 1200                   | kΩ   | $V_{SLP_N} = 5 V$                                                                                                                 |

| RXD (Open-Drain)                     |                                |                     |     |                        | •    |                                                                                                                                   |

| High-level leakage<br>current        | Іцн                            | -5                  |     | 5                      | μΑ   | Normal mode, V <sub>LIN</sub> = V <sub>BAT</sub> , V <sub>RXD</sub> = 5 V                                                         |

| Low-level output current             | I <sub>OL</sub>                | 1.5                 |     |                        | mA   | Normal mode, $V_{LIN} = 0 V$ , $V_{RXD} = 0.4 V$                                                                                  |

| WAKE_N                               |                                |                     |     |                        |      |                                                                                                                                   |

| High-level input voltage             | VIH                            | $V_{\text{BAT}}$ -1 |     | V <sub>BAT</sub> + 0.3 | V    |                                                                                                                                   |

| Low-level input voltage              | VIL                            | -0.3                |     | V <sub>BAT</sub> - 3.3 | V    | Guaranteed by design                                                                                                              |

| High-level input current             | Іін                            | -5                  |     | 5                      | μA   | V <sub>WAKE_N</sub> = 27 V, V <sub>BAT</sub> = 27 V                                                                               |

| Low-level input current              | I.L                            | -30                 |     | -1                     | μA   | $V_{WAKE_N} = 0 V$                                                                                                                |

| INH                                  |                                |                     |     |                        | •    | •                                                                                                                                 |

# Datasheet (EN) 1.1

| Parameters                                                               | Symbol             | Min                   | Тур | Мах                   | Unit | Comments                                                                                                                       |

|--------------------------------------------------------------------------|--------------------|-----------------------|-----|-----------------------|------|--------------------------------------------------------------------------------------------------------------------------------|

| Switch-on resistance<br>Between pins V <sub>BAT</sub> and INH            | $R_{sw(vbat-inh)}$ |                       | 20  | 50                    | Ω    | Switch-on resistance between pins $V_{BAT}$ and INH. Standby, normal, and power-on modes, $I_{INH}$ = -15 mA, $V_{BAT}$ = 12 V |

| High-level leakage<br>current                                            | Іін                | -5                    |     | 5                     | μΑ   | Sleep mode, $V_{INH}$ = 27 V, $V_{BAT}$ = 27 V                                                                                 |

| LIN                                                                      |                    |                       |     |                       |      |                                                                                                                                |

| Current limitation for<br>transmitter dominant<br>state                  | Ibus_lim           | 40                    |     | 110                   | mA   | V <sub>BAT</sub> = 18 V, V <sub>LIN</sub> = 18 V, V <sub>TXD</sub> =0 V                                                        |

| Pull-up resistance                                                       | Rpu                | 50                    |     | 250                   | kΩ   | Sleep mode, $V_{SLP_N} = 0 V$                                                                                                  |

| Receiver recessive input<br>leakage current                              | BUS_PAS_rec        |                       |     | 15                    | μΑ   | V <sub>LIN</sub> = 18 V, V <sub>BAT</sub> = 5.5 V, V <sub>TXD</sub> =5 V                                                       |

| Receiver dominant input<br>Leakage current including<br>pull-up resistor | IBUS_PAS_dom       | -600                  |     |                       | μΑ   | Normal mode, $V_{TXD} = 5 V$<br>$V_{LIN} = 0 V$ , $V_{BAT} = 12 V$                                                             |

| Voltage drop at the serial diode                                         | VSerDiode          | 0.4                   |     | 1                     | v    | Guaranteed by design                                                                                                           |

| Loss-of-ground bus<br>current                                            | Ibus_no_gnd        | -1000                 |     | 10                    | μΑ   | V <sub>BAT</sub> = 12 V, V <sub>LIN</sub> =0 V                                                                                 |

| Loss-of-battery bus<br>current                                           | Ibus_no_bat        |                       |     | 15                    | μΑ   | V <sub>BAT</sub> = 0 V, V <sub>LIN</sub> = 18 V                                                                                |

| Receiver dominant state                                                  | VBUSdom            |                       |     | <b>0.4V</b> BAT       | V    |                                                                                                                                |

| Receiver recessive state                                                 | VBUSrec            | <b>0.6V</b> BAT       |     |                       | V    |                                                                                                                                |

| Receiver center voltage                                                  | Vbus_cnt           | 0.475V <sub>BAT</sub> |     | 0.525V <sub>BAT</sub> | v    | VBUS_CNT = (VBUSrec + VBUSdom) / 2<br>V <sub>BAT</sub> = 7 V to 27 V                                                           |

| Receiver hysteresis<br>voltage                                           | V <sub>HYS</sub>   |                       |     | 0.175V <sub>BAT</sub> | v    | $V_{HYS} = V_{BUSrec} - V_{BUSdom}$                                                                                            |

| Slave Resistance                                                         | Rslave             | 20                    |     | 47                    | kΩ   | Connected between pins LIN and $V_{BAT}$ , $V_{LIN} = 0 V$ , $V_{BAT} = 12 V$                                                  |

| Capacitance on pin LIN                                                   | CLIN               |                       |     | 30                    | pF   | Guaranteed by design                                                                                                           |

| Dominant output voltage                                                  | Vo(dom)            |                       |     | 1.4                   | V    | Normal mode, V <sub>TXD</sub> = 0 V, V <sub>BAT</sub> = 7 V                                                                    |

|                                                                          | v o(dom)           |                       |     | 2.0                   | V    | Normal mode, $V_{TXD} = 0 V$ , $V_{BAT} = 18 V$                                                                                |

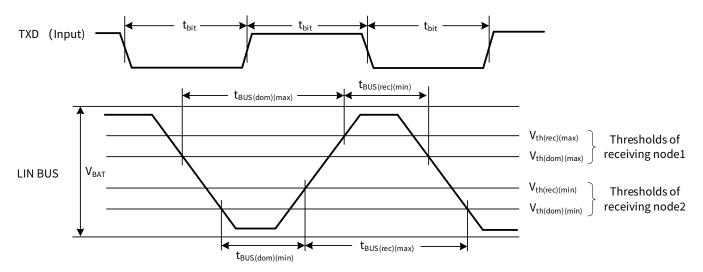

### **6.2.Switching Characteristics**

(V<sub>BAT</sub> = 5.5 V to 18 V,  $T_{vj}$  = -40  $^{\circ}$ C to 150  $^{\circ}$ C. Unless otherwise noted, typical values are at V<sub>BAT</sub> =12 V,  $T_a$  = 25  $^{\circ}$ C).

| Parameters                                                                                                                                               | Symbol            | Min   | Тур | Мах   | Unit | Comments                                                                                                                                                                                                                     |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-----|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <b>Duty cycles</b> (bus load conditions ( $C_{BUS}$ / $R_{BUS}$ ): 1 nF / 1 k $\Omega$ , 6,8 nF / 660 $\Omega$ , 10 nF / 500 $\Omega$ ), see Figure 6. 1 |                   |       |     |       |      |                                                                                                                                                                                                                              |  |  |  |

| Duty Cycle 1                                                                                                                                             | D1 <sup>[1]</sup> | 0.396 |     |       |      | $\begin{split} V_{th(rec)(max)} &= 0.744 \times V_{BAT} \\ V_{th(dom)(max)} &= 0.581 \times V_{BAT} \\ V_{BAT} &= 7 \text{ V to } 18 \text{ V, } t_{bit} = 50  \mu\text{s}^{[2]} \\ ISO 17987 \text{ Param } 27 \end{split}$ |  |  |  |

|                                                                                                                                                          |                   | 0.396 |     |       |      | $\begin{split} V_{th(rec)(max)} &= 0.76 \times V_{BAT} \\ V_{th(dom)(max)} &= 0.593 \times V_{BAT} \\ V_{BAT} &= 5.5 \ V \ to \ 7 \ V, \ t_{bit} = 50 \ \mu s \end{split}$                                                   |  |  |  |

| Duty Cycle 2                                                                                                                                             | D2 <sup>[1]</sup> |       |     | 0.581 |      | $V_{th(rec)(min)} = 0.422 \times V_{BAT}$ $V_{th(dom)(min)} = 0.284 \times V_{BAT}$ $V_{BAT} = 7.6 V \text{ to } 18 \text{ V}, t_{bit} = 50  \mu\text{s}$ ISO 17987 Param 28                                                 |  |  |  |

|                                                                                                                                                          |                   |       |     | 0.581 |      | $\begin{split} V_{th(rec)(min)} &= 0.41 \times V_{BAT} \\ V_{th(dom)(min)} &= 0.275 \times V_{BAT} \\ V_{BAT} &= 6.1 \ V \ to \ 7 \ V, \ t_{bit} = 50 \ \mu s \end{split}$                                                   |  |  |  |

| Duty Cycle 3                                                                                                                                             | D3 <sup>[1]</sup> | 0.417 |     |       |      | $V_{th(rec)(max)} = 0.778 \times V_{BAT}$ $V_{th(dom)(max)} = 0.616 \times V_{BAT}$ $V_{BAT} = 7 V to 18 V, t_{bit} = 96 \ \mu s$ ISO 17987 Param 29                                                                         |  |  |  |

|                                                                                                                                                          |                   | 0.417 |     |       |      | $\begin{split} V_{th(rec)(max)} &= 0.797 \times V_{BAT} \\ V_{th(dom)(max)} &= 0.63 \times V_{BAT} \\ V_{BAT} &= 5.5 \ V \ to \ 7 \ V, \ t_{bit} = 96 \ \mu s \end{split}$                                                   |  |  |  |

| Duty Cycle 4                                                                                                                                             | D4 <sup>[1]</sup> |       |     | 0.59  |      | $\begin{split} V_{th(rec)(min)} &= 0.389 \times V_{BAT} \\ V_{th(dom)(min)} &= 0.251 \times V_{BAT} \\ V_{BAT} &= 7.6 \ V \ to \ 18 \ V, \ t_{bit} = 96 \ \mu s \\ ISO \ 17987 \ Param \ 30 \end{split}$                     |  |  |  |

|                                                                                                                                                          |                   |       |     | 0.59  |      | $\begin{split} V_{th(rec)(min)} &= 0.378 \times V_{BAT} \\ V_{th(dom)(min)} &= 0.242 \times V_{BAT} \\ V_{BAT} &= 6.1 \ V \ to \ 7 \ V, \ t_{bit} = 96 \ \mu s \end{split}$                                                  |  |  |  |

| Timing characteristics                                                                                                                                   |                   |       |     |       |      |                                                                                                                                                                                                                              |  |  |  |

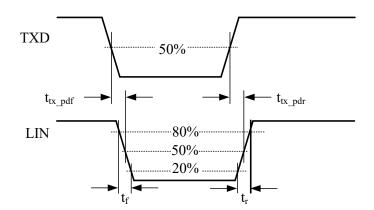

| Fall Time                                                                                                                                                | tr                |       |     | 22.5  | μs   | 20 % - 80 %, see Figure 6. 3                                                                                                                                                                                                 |  |  |  |

| Rise Time                                                                                                                                                | tr                |       |     | 22.5  | μs   | $C_{BUS} = 1 \text{ nF}$ and $R_{BUS} = 1 \text{ k}\Omega$                                                                                                                                                                   |  |  |  |

| Difference between rise and fall time                                                                                                                    | t(r-f)            | -6    |     | 8     | μs   | $C_{BUS}$ = 6.8 nF and $R_{BUS}$ = 660 Ω<br>$C_{BUS}$ = 10 nF and $R_{BUS}$ = 500 Ω                                                                                                                                          |  |  |  |

# Datasheet (EN) 1.1

| Parameters                                    | Symbol                  | Min | Тур | Мах | Unit | Comments                                                                                |

|-----------------------------------------------|-------------------------|-----|-----|-----|------|-----------------------------------------------------------------------------------------|

| Transmitter propagation delay of failing edge | ttx_pdf                 |     |     | 10  | μs   | See Figure 6. 3                                                                         |

| Transmitter propagation delay of rising edge  | ttx_pdr                 |     |     | 10  | μs   | R <sub>BUS</sub> = 500 Ω                                                                |

| Transmitter propagation delay symmetry        | ttx_sym                 | -4  |     | 4.6 | μs   | ttx_sym = ttx_pdr - ttx_pdf                                                             |

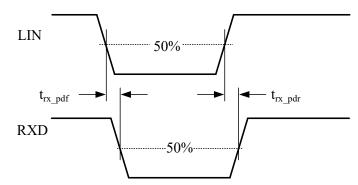

| Receiver propagation delay of failing edge    | trx_pdf                 |     |     | 6   | μs   | See Figure 6. 4                                                                         |

| Receiver propagation delay of rising edge     | trx_pdr                 |     |     | 6   | μs   | $C_{\text{RXD}}$ = 20 $pF^{[3]}$ and $R_{\text{RXD}}$ = 2.4 $k\Omega$                   |

| Receiver propagation<br>delay Symmetry        | trx_sym                 | -2  |     | 2   | μs   | trx_sym = trx_pdr - trx_pdf                                                             |

| LIN dominant wake-up<br>time                  | twake(dom)LIN           | 30  |     | 150 | μs   | Sleep mode                                                                              |

| Dominant wake-up time<br>on pin WAKE_N        | twake(dom)WAKE_N        | 7   |     | 85  | μs   | Sleep mode                                                                              |

| Go to normal time                             | tgotonorm               | 2   |     | 20  | μs   | Time period for mode change<br>from sleep, power-on or standby<br>mode into normal mode |

| Normal mode<br>initialization time            | t <sub>init(norm)</sub> |     |     | 25  | μs   | Normal mode, initialization time                                                        |

| Go to sleep time                              | tgotosleep              | 2   |     | 30  | μs   | Time period for mode change<br>from normal mode into sleep<br>mode                      |

| TXD dominant time-out<br>time                 | tto(dom)TXD             | 27  |     | 90  | ms   | Timer started at falling edge on TXD with $V_{TXD} = 0 V$                               |

$[1] D1, D3=t_{bus(rec)(min)} / (2^{t}t_{bit}), D2, D4=t_{bus(rec)(max)} / (2^{t}t_{bit}), as illustrated in Figure 6.2.$

$\label{eq:tbit} [2] \quad t_{\text{bit}} = 50 \ \mu\text{s} \ (20 \ \text{kbps}), \ t_{\text{bit}} = 96 \ \mu\text{s} \ (10.4 \ \text{kbps}).$

[3] C<sub>RXD</sub> includes load and jig capacitance.

### **6.3.** Parameter Measurement Information

Figure 6. 1 Timing test circuit for LIN transceiver

Figure 6. 2 Timing diagram of LIN transceiver

Figure 6. 3 Propagation delay and transition times from TXD to LIN

Figure 6. 4 Propagation delay and transition times from LIN to RXD

### 7. Function Description

#### 7.1. Overview

The NCA1021S is a LIN transceiver with a low-power mode and multiple wake-up methods. The NCA1021S is fully compatible with the ISO 17987-4 standard. The NCA1021S controls the state of the LIN bus via the TXD pin and reports the state of the bus via its open-drain RXD output pin. An optimized electromagnetic emissions and wave-shaping transmitter is applied in NCA1021S. Therefore, the NCA1021S is providing high electromagnetic immunity and low emissions.

The data rate of the NCA1021S is up to 20 kbps. No external pull-up components are required for slave applications. For master applications, a resistor in the range of 1 k $\Omega$  and a reverse diode must be connected between the LIN bus and the power supply V<sub>BAT</sub> or the INH pin.

The NCA1021S supports three methods for wake-up from sleep mode, by LIN bus, WAKE\_N pin or SLP\_N.

The NCA1021S allows for system-level reductions in battery current consumption by selectively enabling the various power supplies that may be present on a node through the NCA1021S INH output pin.

The NCA1021S provides thermal protection, undervoltage detection, TXD dominant time-out function and loss of power protection. Digital I/O levels compatible for 3.3 V and 5 V microcontrollers.

Figure 7. 1 Block diagram of NCA1021S

### 7.2. Device Functional Modes

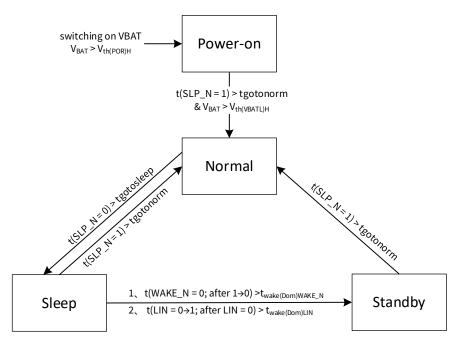

Figure 7. 2 State diagram of NCA1021S

Table 7.1 Function table

| Mode                    | SLP_N | LIN                      | TXD (output) RXD                                                                            |                                              | INH      | Transmitter |  |

|-------------------------|-------|--------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------|----------|-------------|--|

| Power-on <sup>[1]</sup> | low   | pull up by 30 k $\Omega$ | weak pull-down                                                                              | floating                                     | high     | OFF         |  |

| Normal <sup>[2]</sup>   | high  | pull up by 30 k $\Omega$ | HIGH: recessive state<br>LOW: dominant state                                                | HIGH: recessive state<br>LOW: dominant state | high     | ON          |  |

| Sleep                   | low   | weak pull up             | weak pull-down                                                                              | floating                                     | floating | OFF         |  |

| Standby                 | low   | pull up by 30 kΩ         | weak pull-down if<br>remote wake-up,<br>strong pull-down if<br>local wake-up <sup>[3]</sup> | LOW <sup>[4]</sup>                           | high     | OFF         |  |

[1] Power-on mode is entered after switching on V<sub>BAT</sub>.

[2] Normal mode is entered after a positive edge on SLP\_N. If TXD is low, the transmitter is OFF. In the event of a short circuit to ground on pin TXD, the transmitter will be disabled.

[3] The internal wake-up source flag on TXD will be reset after a positive edge on pin SLP\_N.

[4] The wake-up interrupt on pin RXD is released after a positive edge on pin SLP\_N.

#### 7.2.1 Power-on mode

When  $V_{BAT}$  exceeds the power-on-reset threshold voltage  $V_{th(POR)H}$ , the NCA1021S enters power-on mode. Though the NCA1021S is powered-up and INH is high, both the transmitter and receiver are still inactive. If  $t_{(SLP_N=1)} > t_{gotonorm}$ , and  $V_{BAT}$  exceeds the  $V_{th(VBATL)H}$ , the NCA1021S will enter normal mode.

#### 7.2.2 Normal mode

Under the normal mode of NCA1021S, it can receive and send normally on the LIN bus. In the normal mode, In normal mode the transmitter and receiver fully operational. The transmitter receives the signal from the MCU via the TXD, and first determines the dominant timeout, and then converts it into an optimized bus signal slew rate and waveform shaping to minimize EME. The receiver detects the signal on the LIN bus input and transmits it to the microcontroller through the RXD.

The LIN bus has two states: dominant state (voltage near ground) and recessive state (voltage near battery). No external pull-up components are required for slave applications. For a Master application, an external  $1k\Omega$  resistor in series with a diode should be connected between pin INH or V<sub>BAT</sub> and pin LIN, as shown in Figure 8. 1.

#### 7.2.3 Sleep mode

Sleep mode is the lowest power consumption mode of NCA1021S. In sleep mode the transmitter is disabled, releasing the INH to floating state. LIN bus is weakly pulled up, which can prevent false remote wake-up events.

The INH pin is switched to a floating output in sleep mode causing any system power elements controlled by the INH pin to be switched off thus reducing the system power consumption.

The only way to enter sleep mode is to make t  $(SLP_N=0) > t_{gotosleep}$  in normal mode.

The NCA1021S in sleep mode supports three methods to wake up. They are wake-up remotely via LIN bus, and wake-up locally via pin SLP\_N or pin WAKE\_N.

#### 7.2.4 Standby mode

When NCA1021S is in sleep mode, it will enter standby mode by local or remote wake-up by LIN bus or pin WAKE\_N. When a wake-up event occurs and the NCA1021S enters standby mode, the pin RXD is driven low signaling the wake-up event to the controller.

In standby mode, the INH changes from floating to high, which can be used as a control flag for other devices. In standby mode, the LIN bus slave termination resistance, R<sub>slave</sub>, is on.

In Standby mode, the condition of pin TXD indicates the wake-up source when pin SLP\_N is still low. After being remotely awakened by the LIN bus, pin TXD will be in a weak pull-down state. After being woken up locally by the pin WAKE\_N, pin TXD will be in a strong pull-down state.

The NCA1021S exits standby mode and enters normal mode when the pin SLP\_N is set high for longer than tgotonorm.

In standby mode, set the pin SLP\_N high ( $t_{(SLP_N=1)} > t_{gotonorm}$ ) to enter the normal mode. Once the device enters normal mode, the wake-up event is cleared, and the RXD output is released. The RXD output is fully operation and reflects the receiver output from the LIN bus.

#### 7.3. Pin characteristics

#### 7.3.1 RXD

The receiver detects the data stream at the LIN bus input pin and transfers it via pin RXD to the microcontroller. The pin RXD output structure is an open-drain output structure which allows the device to be used with 3.3 V and 5 V microcontrollers. LIN recessive is represented by a high level on the pin RXD and LIN dominant is represented by a low level on the pin RXD. In standby mode, the pin RXD is driven low which can be used as an interrupt for microcontroller. The wake-up interrupt on pin RXD is released after a positive edge on pin SLP\_N. If the microcontrollers RXD pin does not have an integrated pull-up, an external pull-up resistor to the microcontrollers IO supply voltage is required.

#### 7.3.2 SLP\_N

Pin SLP\_N pin controls the functional modes of NCA1021S. When pin SLP\_N is high, NCA1021S operates in normal mode. When SLP\_N is low, NCA1021S operates in sleep mode. Pin SLP\_N has an internal pull-down resistor to ensure the device remains in low power mode even if SLP\_N floats.

#### 7.3.3 WAKE\_N

The NCA1021S can be woken up locally via pin WAKE\_N. Filter at the input of pin WAKE\_N prevents unwanted wake-up events due to automotive transients or EMI.

A falling edge at pin WAKE\_N followed by  $t_{(WAKE_N=0)} > t_{wake(dom)WAKE_N}$  results in a local wake-up. The pin WAKE\_N internally pulls up to  $V_{BAT}$ .

#### 7.3.4 TXD

TXD is the interface to the MCU LIN protocol controller that is used to control the state of the LIN output. When TXD is high, the LIN output is recessive. When the TXD is low, the LIN output is dominant. Pin TXD provides a pull-down to GND to force a predefined level on input pin TXD in case the pin TXD is unsupplied. In Standby mode, the status of pin TXD indicates the wake-up source: weak pull-down for a remote wake-up request and strong pull-down for a local wake-up request.

After switching to normal mode, the NCA1021S will detect the status of TXD. The LIN driver will be enabled only if a high TXD level is detected.

#### 7.3.5 LIN

LIN has two internal pull-up resistors to  $V_{BAT}$ . In sleep mode, the internal slave termination between pins LIN and  $V_{BAT}$  is disabled to minimize the power dissipation. Only a weak pull-up between pins LIN and  $V_{BAT}$  is present. There is an internal slave termination resistor between pin LIN and pin  $V_{BAT}$ . For master applications, an external 1 k $\Omega$  pull-up resistor with series blocking diode can be used.

A falling edge at pin LIN followed by a low level maintained for a certain time ( $t_{wake(dom)LIN}$ ) and a rising edge at pin LIN respectively results in a remote wake-up.

#### 7.3.6 VBAT

$V_{BAT}$  pin is responsible for the input of the power supply. Even if there is a loss of power, the NCA1021S has extremely low leakage form the pin LIN, which will not pull the LIN bus down. The recommended voltage range for  $V_{BAT}$  is 5.5 V to 27 V. If  $V_{BAT} < 5.5$  V or  $V_{BAT} > 27$  V, the NCA1021S may remain operational, but parameter values cannot be guaranteed.

#### 7.3.7 INH

Pin INH is battery related inhibit output for controlling an external voltage regulator. Only in sleep mode INH is floating, the rest is high. As a result of the high condition on pin INH the voltage regulator and the microcontroller can be activated.

#### 7.4. TXD dominant time-out function

During normal mode, a TXD dominant time-out timer circuit in NCA1021S prevents the local node from blocking network communication in event of a hardware or software failure where TXD is held dominant longer than the time-out period  $t_{to(dom)TXD}$ . The timer is triggered by a negative edge on pin TXD. If the duration of the low-level on pin TXD exceeds the internal timer value  $(t_{to(dom)TXD})$ , the transmitter is disabled, driving the bus line into a recessive state. The timer is reset by a positive edge on pin TXD.

#### 7.5. Fail-safe features

The current of the transmitter output stage is limited to protect the transmitter against short circuit to pins V<sub>BAT</sub> or GND.

In automotive applications, some LIN transceivers in a system can be unpowered or ignition supplied, while others in the network remains powered by the battery. A loss of power (pins V<sub>BAT</sub> and GND) has no impact on the LIN bus line and the microcontroller. There are no reverse currents from the bus.

The transmitter at pin LIN is protected against overtemperature conditions. If the junction temperature exceeds the shutdown junction temperature  $T_{j(sd)}$ , the thermal protection circuit disables the transmitter. Once the over temperature fault condition has been removed and the junction temperature has cooled beyond the hysteresis temperature, the transmitter is re-enabled.

If  $V_{BAT}$  drops below  $V_{th(VBATL)L}$ , a protection circuit disables the transmitter. The transmitter is enabled again when  $V_{BAT} > V_{th(VBATL)H}$ .

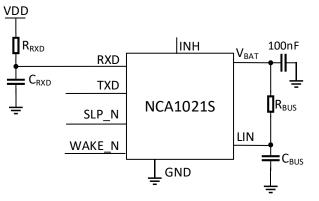

### 8. Application Note

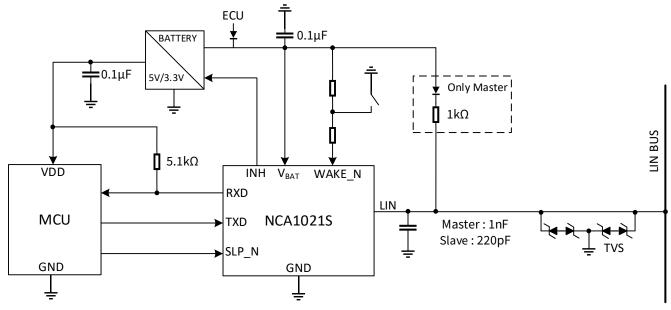

### 8.1. Typical Application

The Figure 8. 1 is the basic schematic of NCA1021S. The NCA1021S requires a 0.1  $\mu$ F bypass capacitors between V<sub>BAT</sub> and GND. The bypass capacitance value can also be determined according to the actual situation of the system. The capacitor should be placed as close as possible to the package.

For a Master application, an external  $1k\Omega$  resistor in series with a diode should be connected between pin INH or V<sub>BAT</sub> and pin LIN. If RXD on the MCU does not have an internal pull-up, an external pull-up resistor is required.

The LIN external capacitance value is selected according to the actual situation (refer to ISO 17987-4:2016 5.3.6 Line characteristics), generally 220 pF for the slave or 1nF for the master. To alleviate EMI problems, EMI filtering of LIN bus is strongly recommended, which is also a necessary measure. In addition to LIN message itself will radiate noise through rising edge, falling edge and asymmetric waveform, noise from other parts of the car may also penetrate LIN bus. Usually, a ferrite bead or inductor can be connected in series on the LIN bus.

Transient pulse suppression is also important for LIN buses, so it is recommended to add bidirectional TVS tubes.

Figure 8. 1 Basic schematic of NCA1021S

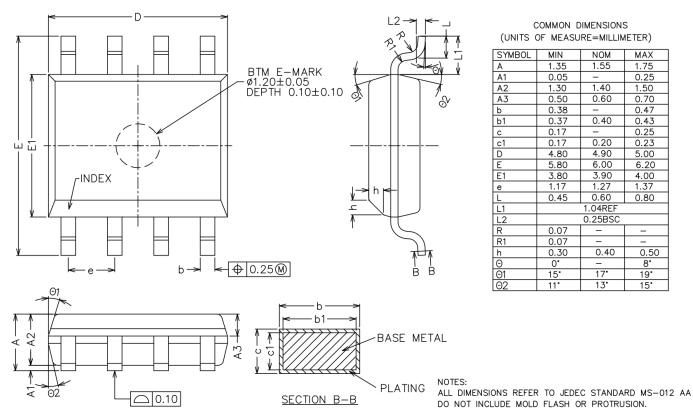

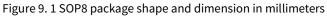

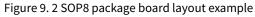

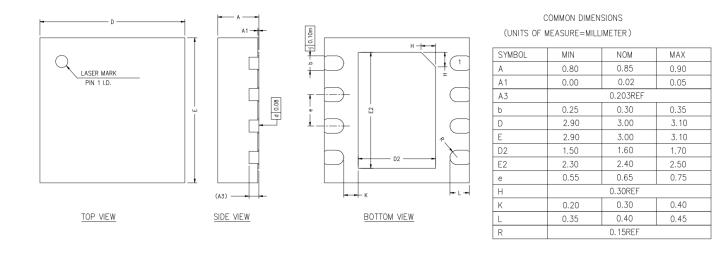

### 9. Package Information

# Datasheet (EN) 1.1

SIDE VIEW

NOTES: ALL DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSION.

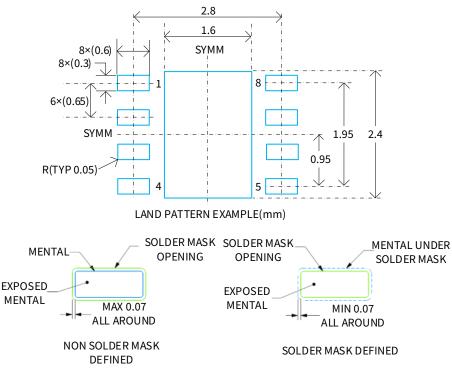

#### Figure 9. 3 DFN8 package shape and dimension in millimeters

Figure 9. 4 DFN8 package board layout example

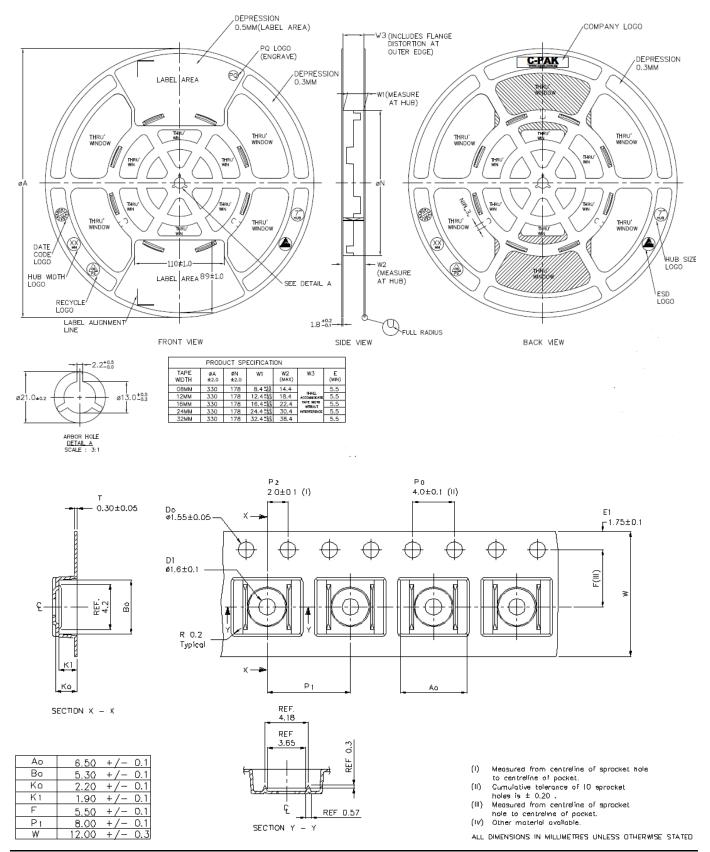

### **10. Order Information**

| Part Number       | Max Data Rate (kbps) | Junction Temperature | MSL | Package | SPQ  |

|-------------------|----------------------|----------------------|-----|---------|------|

| NCA1021S-Q1SPR    | 20                   | -40 °C to 150 °C     | 1   | SOP8    | 2500 |

| NCA1021S-Q1DNR 20 |                      | -40 °C to 150 °C     | 1   | DFN8    | 5000 |

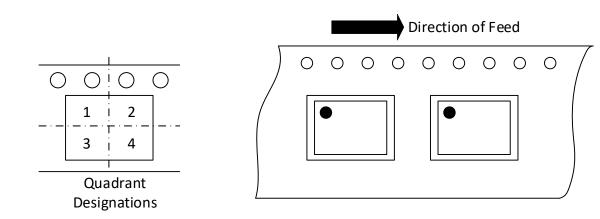

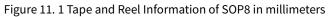

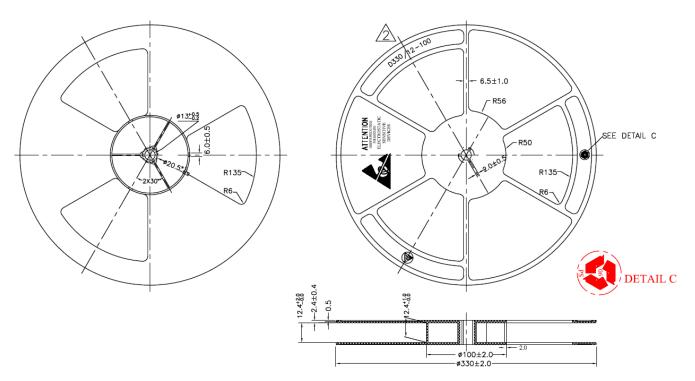

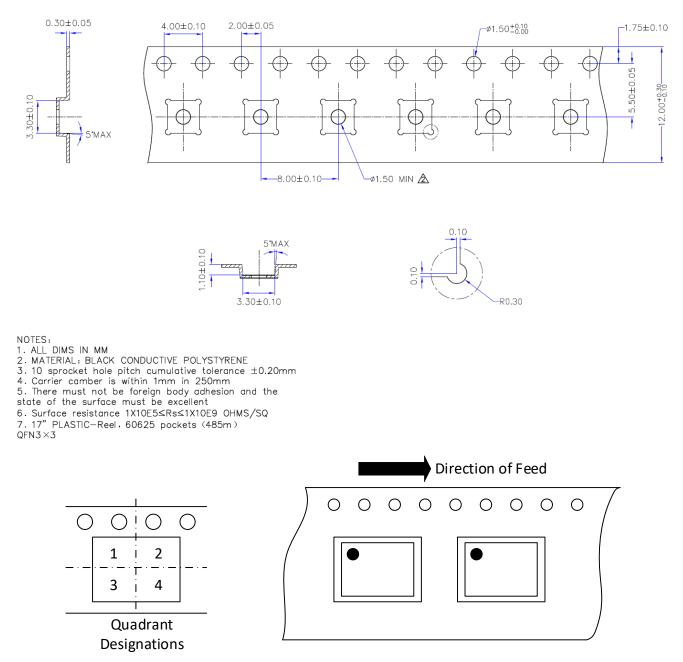

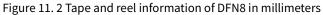

### **11. Tape and Reel Information**

Copyright © 2024, NOVOSENSE

# Datasheet (EN) 1.1

## 12. Revision History

| Revision | Description                                                | Date       |

|----------|------------------------------------------------------------|------------|

| 1.0      | Initial version                                            | 2023/12/11 |

|          | Added restriction for V <sub>BUS_CNT</sub> .               |            |

|          | Corrected condition for t <sub>wake(dom)WAKE_N</sub> .     |            |

|          | Replace commander and responder with master and slave.     |            |

| 1.1      | Updated the description of the master node in section 8.1. | 2024/4/19  |

|          | Updated Figure 8. 1.                                       |            |

|          | Updated SOP8 package board layout example.                 |            |

|          | Added DFN8 package board layout example.                   |            |

### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as any warranty or authorization of, express or implied, including but not limited to accuracy, completeness, merchantability, fitness for a particular purpose or infringement of any third party's intellectual property rights.

You are solely responsible for your use of Novosense' products and applications, and for the safety thereof. You shall comply with all laws, regulations and requirements related to Novosense's products and applications, although information or support related to any application may still be provided by Novosense.

The resources are intended only for skilled developers designing with Novosense' products. Novosense reserves the rights to make corrections, modifications, enhancements, improvements or other changes to the products and services provided. Novosense authorizes you to use these resources exclusively for the development of relevant applications designed to integrate Novosense's products. Using these resources for any other purpose, or any unauthorized reproduction or display of these resources is strictly prohibited. Novosense shall not be liable for any claims, damages, costs, losses or liabilities arising out of the use of these resources.

For further information on applications, products and technologies, please contact Novosense (www.novosns.com).

#### Suzhou Novosense Microelectronics Co., Ltd